资料下载

基于FPGA水声信号采集存储系统的设计

水声信号采集存储系统是海洋环境调查仪器的重要组成部分。开展水声环境调查所使用的海洋仪器要求设备通道多、同步性好、采样率高、数据存储容量大。市场上常见的数据采集器多是采集某些固定种类的信号,动态范围比较小,通道数一般也比较少,有些还要求与主机进行接口等,这些都限制了其在水声信号采集中的应用。为满足需要,本文设计了适合于水声数据采集存储的较为通用的系统,系统单板具有8个采集通道,多个单板级联可实现多通道同步采集、USB高速存储。

1 总体设计

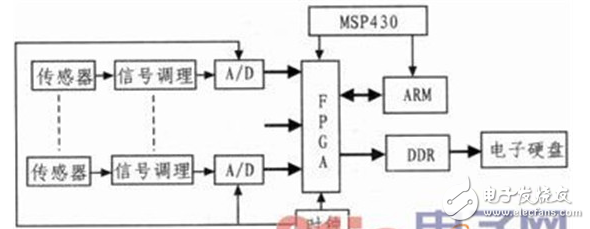

该系统总体结构如图1所示,上级电路通过级联接口发送采集指令,单片机初始化控制FPGA,控制FPGA首先判断单板是否为级联单板,再初始化相应的FPGA。采集模块的FPGA向需要同步采集的通道对应的A/D芯片提供统一的时钟,使得A/D同步的选择相应的通道进行数据的同步采样和转换,其结果传给负责缓存的FPGA,缓存在DDR对应的存储空间,然后由ARM控制存储模块的FPGA从DDR空间读取数据进行本地存储。

2 系统硬件设计

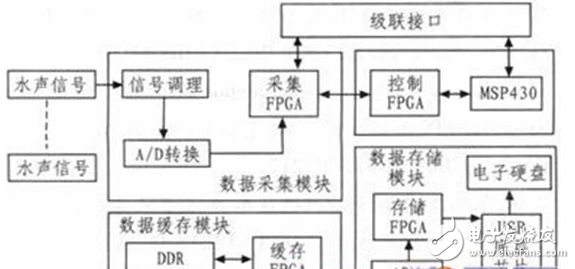

系统硬件主要由控制模块、数据采集模块、缓存模块、存储模块几部分组成,系统硬件结构图如图2所示。单片机功耗低、接口丰富、可靠性高,被系统用做上电引导芯片;FPGA器件具有集成度高、内部资源丰富、特别适合处理多路并行数据等明显优于普通微处理器的特点,所以系统采用XILINX公司不同型号的FPGA作为不同模块的主控芯片。针对系统设计中对采集存储实时性和同步性的要求,存储模块采用FPGA与ARM相结合的设计,采集主控制逻辑用ARM实现,FPGA负责数据的高速传输和存储。

控制模块相当于系统的值班电路,当系统作为从板工作时,只有控制模块和数据采集模块带电,其他模块关闭。由于FPGA内核电压只有1.2 V,在这种情况下系统工作电流不大于1 A,低功耗的设计保证系统可在无人值守的情况下长时间连续进行采集存储工作。系统需要多通道数据同时采集存储时,用户通过配置主板的控制模块参数设定8、16或32通道采集,主控FPGA通过级联接口发送统一的采集时钟到系统从板,从而实现系统多通道水声信号的同步采集及存储。另外,通过单片机接口也可以随时监控系统工作状态,系统具有修复功能,采集存储过程中出现错误时,可根据用户配置自动进行相应的错误处理。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章