资料下载

×

SPI接口的应用与基于FPGA的SPI自动发送模块设计

消耗积分:0 |

格式:rar |

大小:0.3 MB |

2017-10-19

SPI 接口应用十分广泛,在很多情况下,人们会用软件模拟的方法来产生SPI 时序或是采用带SPI 功能模块的MCU。但随着可编程逻辑技术的发展,人们往往需要自己设计简单的SPI 发送模块。本文介绍一种基于FPGA 的将并行数据以SPI 串行方式自动发送出去的方法。

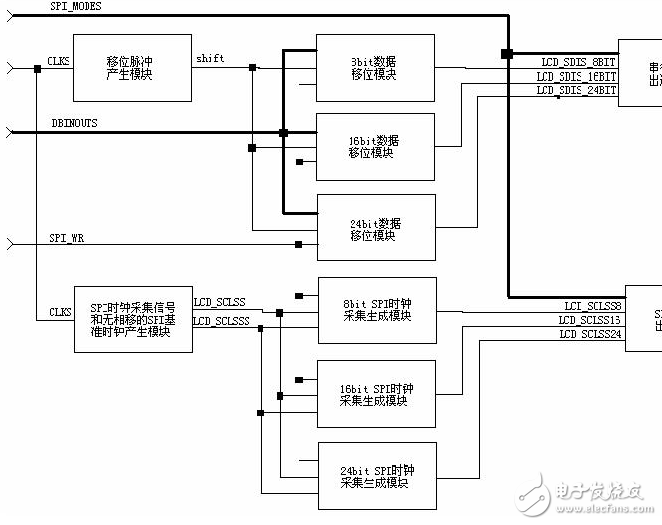

二、关键字:

VHDL、FPGA、SPI、串行数据输出选择模块、移位脉冲产生模块、SPI 时钟采集信号和无相移的SPI 基准时钟产生模块、SPI 时钟输出选择模块、8bit SPI 时钟采集生成模块、16bit SPI 时钟采集生成模块、24bit SPI 时钟采集生成模块、8bit 数据移位模块、16bit 数据移位模块、24bit 数据移位模块。

三、功能框图:

SPI_MODES 为输入模式选择端口:

--“01”is 8bit 传输模式

--“10”is 16bit 传输模式

--“11”is 24bit 传输模式

CLKS 为整个模块的基准时钟

DBINOUTS 为并行数据输入端口:

--8bit 模式为DBINOUTS(7 downto 0)

--16bit 模式为DBINOUTS(15 downto 0)

--24bit 模式为DBINOUTS(23 downto 0)

SPI_WR 为启动SPI 传输的信号

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章