资料下载

×

基于DSP的视频采集存储系统的设计方案

消耗积分:1 |

格式:rar |

大小:0.3 MB |

2017-10-29

数字图象处理技术在电子通信与信息处理领域得到了广泛的应用,设计一种功能灵活、使用方便、便于嵌入到系统中的视频信号采集电路具有重要的实用意义。

在研究基于DSP的视频监控系统时,考虑到高速实时处理及实用化两方面的具体要求,需要开发一种具有高速、高集成度等特点的视频图象信号采集系统,为此系统采用专用视频解码芯片和复杂可编程逻辑器件(CPLD)构成前端图象采集部分。设计上采用专用视频解码芯片,以CPLD器件作为控制单元和外围接口,以FIFO为缓存结构,能够有效地实现视频信号的采集与读取的高速并行,具有整体电路简单、可靠性高、集成度高、接口方便等优点,无需更改硬件电路,就可以应用于各种视频信号处理系统中。使得原来非常复杂的电路设计得到了极大的简化,并且使原来纯硬件的设计,变成软件和硬件的混合设计,使整个系统的设计增加柔韧性。

1 系统硬件平台结构

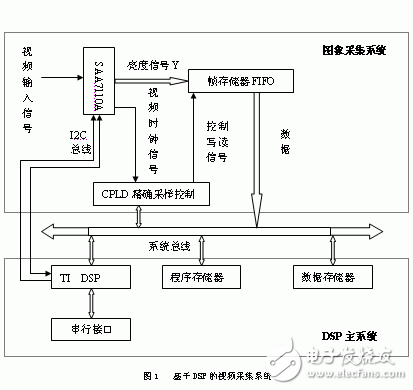

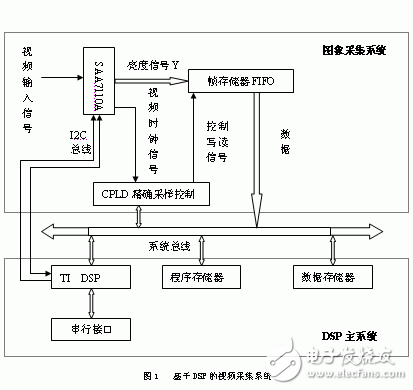

系统平台硬件结构如图1所示。整个系统分为两部分,分别是图象采集系统和基于DSP主系统。前者是一个基于SAA7110A/SAA7110视频解码芯片,由复杂可编程逻辑芯片CPLD实现精确采样的高速视频采集系统;后者是通用数字信号处理系统,它主要包括:64K WORD程序存储器、64K WORD数据存储器、DSP、时钟产生电路、串行接口及相应的电平转换电路等。

系统的工作流程是,首先由图象采集系统按QCIF格式精确采集指定区域的视频图象数据,暂存于帧存储器FIFO中;由DSP将暂存于FIFO中的数据读入DSP的数据存储器中,与原先的几帧图象数据一起进行基于H.263的视频数据压缩;然后由DSP将压缩后的视频数据平滑地从串行接口输出,由普通MODEM或ADSL MODEM传送到远端的监控中心,监控中心的PC机收到数据后进行相应的解码,并将还原后的视频图象进行显示或进行基于WEB的广播。

2 视频信号采集系统

2.1 视频信号采集系统的基本特性

一般的视频信号采集系统一般由视频信号经箝位放大、同步信号分离、亮度/色度信号分离和A/D变换等部分组成,采样数据按照一定的时序和总线要求,输出到数据总线上,从而完成视频信号的解码,图中的存储器作为帧采样缓冲存储器,可以适应不同总线、输出格式和时序要求的总线接口。

视频信号采集系统是高速数据采集系统的一个特例。过去的视频信号采集系统采用小规模数字和模拟器件,来实现高速运算放大、同步信号分离、亮度/色度信号分离、高速A/D变换、锁相环、时序逻辑控制等电路的功能。但由于系统的采样频率和工作时钟高达数十兆赫兹,且器件集成度低,布线复杂,级间和器件间耦合干扰大,因此开发和调试都十分困难;另一方面,为达到精确采样的目的,采样时钟需要和输人的视频信号构成同步关系,因而,利用分离出来的同步信号和系统采样时钟进行锁相,产生精确同步的采样时钟,成为设计和调试过程中的另一个难点。同时,通过实现亮度、色度、对比度、视频前级放大增益的可编程控制,达到视频信号采集的智能化,又是以往系统难以完成的。关于这一点,在系统初期开发过程中已有深切体会[1]。

基于以上考虑,本系统采用了SAA7110A作为视频监控系统的输入前端视频采样处理器。

2.2 视频图象采集系统设计

SAA7110/SAA7110A是高集成度、功能完善的大规模视频解码集成电路[2]。它采用PLCC68封装,内部集成了视频信号采样所需的2个8bit模/数转换器,时钟产生电路和亮度、对比度、饱和度控制等外围电路,用它来替代原来的分立电路,极大地减小系统设计的工作量,并通过内置的大量功能电路和控制寄存器来实现功能的灵活配置。SAA7110/SAA7110A可应用的范围包括桌面视频、多媒体、数字电视机、图象处理、可视电话、视频图象采集系统等领域。

SAA7110/SAA7110A的控制总线接口为I2C总线。SAA7110/SAA7110A作为I2C总线的从器件,根据SA管脚的电平,器件的读写地址可以分别设置为9CH/9DH(W/R,SA=0)或9DH/9FH(W/R,SA=1)。其内部共计47个寄存器,分别控制解码器(00H~19H)和视频接口(20H~34H)。通过I2C总线读、写片内的上述寄存器,可以完成输入通道选择、电平箝位和增益控制、亮度、色度和饱和度控制等功能。

但是,有一个问题必须解决,那就是DSP芯片没有内置I2C总线接口,为此,本系统提出并采用了对DSP芯片的两个可编程I/O引脚进行软件仿真来实现I2C总线控制的方法。由于受C2000程序存储空间最大仅有64KB的限制,为了减小I2C总线控制仿真软件的规模,仿真软件全部用汇编语言完成,因而给本系统的设计带来了相当的难度和工作量。

在研究基于DSP的视频监控系统时,考虑到高速实时处理及实用化两方面的具体要求,需要开发一种具有高速、高集成度等特点的视频图象信号采集系统,为此系统采用专用视频解码芯片和复杂可编程逻辑器件(CPLD)构成前端图象采集部分。设计上采用专用视频解码芯片,以CPLD器件作为控制单元和外围接口,以FIFO为缓存结构,能够有效地实现视频信号的采集与读取的高速并行,具有整体电路简单、可靠性高、集成度高、接口方便等优点,无需更改硬件电路,就可以应用于各种视频信号处理系统中。使得原来非常复杂的电路设计得到了极大的简化,并且使原来纯硬件的设计,变成软件和硬件的混合设计,使整个系统的设计增加柔韧性。

1 系统硬件平台结构

系统平台硬件结构如图1所示。整个系统分为两部分,分别是图象采集系统和基于DSP主系统。前者是一个基于SAA7110A/SAA7110视频解码芯片,由复杂可编程逻辑芯片CPLD实现精确采样的高速视频采集系统;后者是通用数字信号处理系统,它主要包括:64K WORD程序存储器、64K WORD数据存储器、DSP、时钟产生电路、串行接口及相应的电平转换电路等。

系统的工作流程是,首先由图象采集系统按QCIF格式精确采集指定区域的视频图象数据,暂存于帧存储器FIFO中;由DSP将暂存于FIFO中的数据读入DSP的数据存储器中,与原先的几帧图象数据一起进行基于H.263的视频数据压缩;然后由DSP将压缩后的视频数据平滑地从串行接口输出,由普通MODEM或ADSL MODEM传送到远端的监控中心,监控中心的PC机收到数据后进行相应的解码,并将还原后的视频图象进行显示或进行基于WEB的广播。

2 视频信号采集系统

2.1 视频信号采集系统的基本特性

一般的视频信号采集系统一般由视频信号经箝位放大、同步信号分离、亮度/色度信号分离和A/D变换等部分组成,采样数据按照一定的时序和总线要求,输出到数据总线上,从而完成视频信号的解码,图中的存储器作为帧采样缓冲存储器,可以适应不同总线、输出格式和时序要求的总线接口。

视频信号采集系统是高速数据采集系统的一个特例。过去的视频信号采集系统采用小规模数字和模拟器件,来实现高速运算放大、同步信号分离、亮度/色度信号分离、高速A/D变换、锁相环、时序逻辑控制等电路的功能。但由于系统的采样频率和工作时钟高达数十兆赫兹,且器件集成度低,布线复杂,级间和器件间耦合干扰大,因此开发和调试都十分困难;另一方面,为达到精确采样的目的,采样时钟需要和输人的视频信号构成同步关系,因而,利用分离出来的同步信号和系统采样时钟进行锁相,产生精确同步的采样时钟,成为设计和调试过程中的另一个难点。同时,通过实现亮度、色度、对比度、视频前级放大增益的可编程控制,达到视频信号采集的智能化,又是以往系统难以完成的。关于这一点,在系统初期开发过程中已有深切体会[1]。

基于以上考虑,本系统采用了SAA7110A作为视频监控系统的输入前端视频采样处理器。

2.2 视频图象采集系统设计

SAA7110/SAA7110A是高集成度、功能完善的大规模视频解码集成电路[2]。它采用PLCC68封装,内部集成了视频信号采样所需的2个8bit模/数转换器,时钟产生电路和亮度、对比度、饱和度控制等外围电路,用它来替代原来的分立电路,极大地减小系统设计的工作量,并通过内置的大量功能电路和控制寄存器来实现功能的灵活配置。SAA7110/SAA7110A可应用的范围包括桌面视频、多媒体、数字电视机、图象处理、可视电话、视频图象采集系统等领域。

SAA7110/SAA7110A的控制总线接口为I2C总线。SAA7110/SAA7110A作为I2C总线的从器件,根据SA管脚的电平,器件的读写地址可以分别设置为9CH/9DH(W/R,SA=0)或9DH/9FH(W/R,SA=1)。其内部共计47个寄存器,分别控制解码器(00H~19H)和视频接口(20H~34H)。通过I2C总线读、写片内的上述寄存器,可以完成输入通道选择、电平箝位和增益控制、亮度、色度和饱和度控制等功能。

但是,有一个问题必须解决,那就是DSP芯片没有内置I2C总线接口,为此,本系统提出并采用了对DSP芯片的两个可编程I/O引脚进行软件仿真来实现I2C总线控制的方法。由于受C2000程序存储空间最大仅有64KB的限制,为了减小I2C总线控制仿真软件的规模,仿真软件全部用汇编语言完成,因而给本系统的设计带来了相当的难度和工作量。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章