资料下载

基于PCI桥接IP Core的VeriIog HDL实现

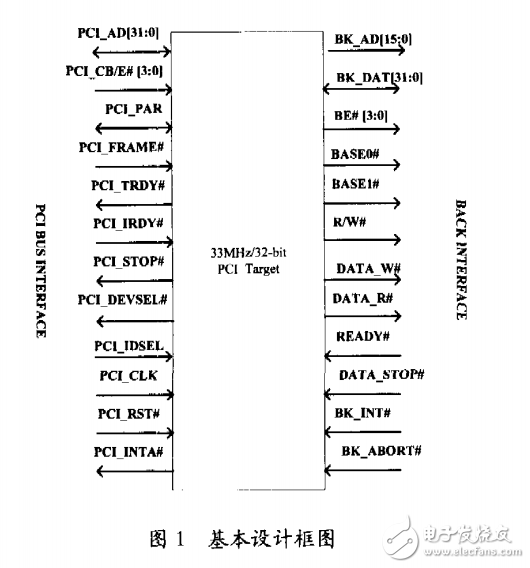

PCI总线具有高数据传输率、独立于处理器、并且支持多功能外设等一系列独特的性能,越来越受到各行业的重视 ,使得 PCI总线接 口非常普及 ,但是仍然有很多非 PCI接口的设备存在,这就需要通过具有 PCI桥接功能的IPCore来实现总线协议的转接,从而完成设备本身的功能。2 PCIV2.2简介PCI总线如果只作为 目标设备至少需要47条接口信号线,如果作为主设备则至少需要 49条,也就是要加上一个 REQ}}和 GNT#来进行仲裁判断。其中这些信号线主要包括数据/地址线、接口控制线、仲裁、总线命令以及系统信号线。对于 32bit的信号宽度,一次数据交易都是由一个地址周期和一 个或者几个数据周期组成的。在每个 PCI交程中,主要的控制信号有:帧周期信号 FRAME#、字节使能 C/BE#、主设备准备好信号 IRDY#、目标设备准备好信号 TRDY#、设备选择信号 DESEL#。利用这些信号便可处理数据、地址、实现接口控制、仲裁及系统功能。PCI总线传输的几个基本特点:(1)数据传输 时主设 备驱动 AD 上 的地址和C/BE#上的命令 ,同时主设备有效 FRAME#表 明交易开始。而总线上的所有 目标开始采样地址命令和FRAME#,并开始译码确定是不是对本机 的访问,同时从命令字中识别该交易是读操作还是写操作 ;(2)读写交易根据控制信号 IRDY#,TRDY#,DESEL#以及 FRAME#的状态来控制交易的进行和终止;(3)如果对于主设备或者 目标设备 中的任何一个没有足够的能力来完成交易则可以通过插入等待周期来中断本次交

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章