资料下载

Verilog HDL的基础知识详细说明

硬件描述语言基本语法和实践

(1)VHDL 和Verilog HDL的各自特点和应用范围

(2)Verilog HDL基本结构语言要素与语法规则

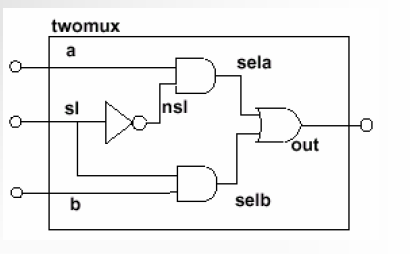

(3) Verilog HDL组合逻辑语句结构

(4) Verilog HDL时序逻辑语句结构

(5)Verilog HDL 程序设计中需要注意的问题。

(6)上机实践(Verilog HDL/VHDL)

具有特殊结构能够对硬件逻辑电路的功能进行描

述的一种高级编程语言

这种特殊结构能够:

描述电路的连接

描述电路的功能

在不同抽象级上描述电路

描述电路的时序

表达具有并行性

v HDL主要有两种:Verilog和VHDL

Verilog起源于C语言,因此非常类似于C语言,容易掌握

VHDL起源于ADA语言,格式严谨,不易学习。

VHDL出现较晚,但标准化早。IEEE 1706-1985标准。

使用HDL描述设计具有下列优点:

设计在高层次进行,与具体实现无关

设计开发更加容易

早在设计期间就能发现问题

能够自动的将高级描述映射到具体工艺实现

在具体实现时才做出某些决定

HDL具有更大的灵活性

可重用

可以选择工具及生产厂

HDL能够利用先进的软件

更快的输入

易于管理

由于Verilog HDL 早在1983 年就已推出至今已有十三年的历史因而拥有广泛的设计群体,成熟的资源比VHDL丰富。而Verilog与VHDL相比最大的优点是它是一种非常容易掌握的硬件描述语言而掌握设计技术,而掌握VHDL就比较困难

目前版本的Verilog HDL 和 VHDL在行为级抽象建模的覆盖范围方面也有所不同。一般认为Verilog HDL 在系统描述方面比VHDL强一些。Verilog HDL 较为适合算法级,寄存器传输级,逻辑级,门级设计。而VHDL更为适合特大型的系统级设计

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章