资料下载

×

FPGA+DSP的雷达回波发生器设计解析

消耗积分:1 |

格式:rar |

大小:0.3 MB |

2017-11-01

在研制各种实用雷达的过程中,需要通过多次实验来检验雷达对目标回波信号的分析处理能力。由于开发环境和实验条件的限制,雷达系统中各部件及整个系统的测试非常困难,受天气状况等因素的影响,其性能及指标测试难以在完全真实的环境中进行。因此,通过数字模拟的方法真实地模拟雷达回波信号很有意义。雷达回波发生器是数字仿真技术和雷达技术相结合的产物,它通过仿真模拟的方法产生目标和环境信息的回波信号。利用这种回波信号对雷达信号处理机进行调试、分析和评估,已成为现代雷达信号处理机研制和生产的重要手段。

采用DSP和FPGA/CPLD相结合的系统结构综合了两者在系统控制和实时数字信号处理方面的优势,结构灵活、实现性强[1]。本文提出了一种以FPGA为核心,DSP实时控制,外加PROM、Flash、CPLD以及D/A等外围电路构成的雷达中频回波信号发生器的设计方法,可以通过在线编程在相同的硬件平台上实现不同体制、多目标的雷达回波。

1 雷达回波发生器方案设计

1.1 系统性能要求

本雷达回波发生器是为了对雷达信号处理机进行测试、评估以及新的信号处理算法而开发研制的,因而在设计上要满足通用性要求,能模拟产生不同体制雷达的回波信号[2]。通用性设计要求硬件外围接口电路尽可能简单,对各种电平规范具有兼容性;所选器件适应性强,通过重配置可编程逻辑电路即可产生不同带宽、不同时宽的雷达信号而不用修改硬件设计[3-4]。同时,为了真实地反映雷达目标的复杂环境,要求雷达回波发生器能加入噪声和干扰,从而能够对信号处理机进行全面的评估和检测。

本雷达回波发生器要求能选择产生单脉冲跟踪、DBF、SAR 3种体制雷达的最多3个目标的回波信号,雷达波形为简单脉冲、线性调频信号、相位编码信号可选。主要技术指标如下:

(1)中频载频频率:30 MHz;

(2)系统基准时钟:10 MHz;

(3)波形存储深度为10 K,信号采样率100 MHz;

(4)幅度分辨率为12 bit;

(5)频率范围为0.37 Hz~25 MHz,频率分辨率为0.37 Hz;

(6)输出模拟信号幅度范围为±2.5 V;

(7)DBF体制时天线阵元数为16个。

1.2 系统实现方案

雷达回波发生器的实现有以下3种方法:全硬件实现、微机+D/A插卡实现以及微机+模拟器DSP组合实现。由于全硬件实现时硬件设计过于复杂、灵活性差、微机+D/A插卡方法受D/A数据传输率的限制,所以目前雷达回波发生器的设计中,多采用微机+模拟器DSP组合方法。该方法灵活性好、数据量适中、易扩充、满足通用性要求[5]。

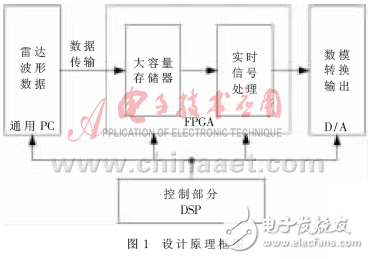

通过对几种回波发生器实现方法的比较,结合本雷达回波发生器要实现的功能以及灵活性、通用性的设计思想,本文提出了一种新的雷达中频回波发生器的设计与实现方法。该方法严格说仍属于微机+模拟器DSP组合方法,但采用了微机+FPGA+DSP+D/A的组合,如图1所示。

采用DSP和FPGA/CPLD相结合的系统结构综合了两者在系统控制和实时数字信号处理方面的优势,结构灵活、实现性强[1]。本文提出了一种以FPGA为核心,DSP实时控制,外加PROM、Flash、CPLD以及D/A等外围电路构成的雷达中频回波信号发生器的设计方法,可以通过在线编程在相同的硬件平台上实现不同体制、多目标的雷达回波。

1 雷达回波发生器方案设计

1.1 系统性能要求

本雷达回波发生器是为了对雷达信号处理机进行测试、评估以及新的信号处理算法而开发研制的,因而在设计上要满足通用性要求,能模拟产生不同体制雷达的回波信号[2]。通用性设计要求硬件外围接口电路尽可能简单,对各种电平规范具有兼容性;所选器件适应性强,通过重配置可编程逻辑电路即可产生不同带宽、不同时宽的雷达信号而不用修改硬件设计[3-4]。同时,为了真实地反映雷达目标的复杂环境,要求雷达回波发生器能加入噪声和干扰,从而能够对信号处理机进行全面的评估和检测。

本雷达回波发生器要求能选择产生单脉冲跟踪、DBF、SAR 3种体制雷达的最多3个目标的回波信号,雷达波形为简单脉冲、线性调频信号、相位编码信号可选。主要技术指标如下:

(1)中频载频频率:30 MHz;

(2)系统基准时钟:10 MHz;

(3)波形存储深度为10 K,信号采样率100 MHz;

(4)幅度分辨率为12 bit;

(5)频率范围为0.37 Hz~25 MHz,频率分辨率为0.37 Hz;

(6)输出模拟信号幅度范围为±2.5 V;

(7)DBF体制时天线阵元数为16个。

1.2 系统实现方案

雷达回波发生器的实现有以下3种方法:全硬件实现、微机+D/A插卡实现以及微机+模拟器DSP组合实现。由于全硬件实现时硬件设计过于复杂、灵活性差、微机+D/A插卡方法受D/A数据传输率的限制,所以目前雷达回波发生器的设计中,多采用微机+模拟器DSP组合方法。该方法灵活性好、数据量适中、易扩充、满足通用性要求[5]。

通过对几种回波发生器实现方法的比较,结合本雷达回波发生器要实现的功能以及灵活性、通用性的设计思想,本文提出了一种新的雷达中频回波发生器的设计与实现方法。该方法严格说仍属于微机+模拟器DSP组合方法,但采用了微机+FPGA+DSP+D/A的组合,如图1所示。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章