资料下载

×

DSP和USB的高速数据采集与处理系统设计方案

消耗积分:1 |

格式:rar |

大小:0.5 MB |

2017-11-06

在图像数据处理系统中,常常需要对高速信号进行采集与处理。例如,在光传感技术中对光脉冲散射信号的测量,在雷达工程中对电磁脉冲信号的测量等,都需要对高速信号进行采集与运算,而且此类高速信号的测量,往往对数据采集与处理系统提出严格的要求。本文设计并实现一种基于DSP和USB的高速数据采集与处理系统。该系统电路简单,可靠性好,具有一定的通用性,并且可以进行多通道扩展。

1 原理概述

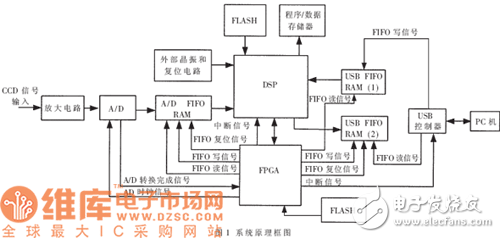

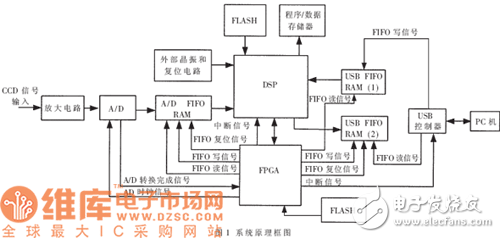

基于DSP和USB的高速数据采集与处理系统的原理框图如图1所示。系统上电后,DSP、FPGA分别由各自的FLASH加载程序,采集与处理系统开始运行。在A/D变换器完成转换后由FPGA向DSP发送中断0申请信号,DSP从A/D FIFO RAM中读取数据,并进行小波变换去噪处理,处理结束后DSP向USB控制器发送中断申请信号,USB控制器将处理后的数据发送至PC机,由主机应用程序显示数据。主机应用程序还可以对整个采集、处理系统进行控制,主要设定三个功能:接收处理后的数据,接收处理前的数据,设定A/D的采样频率和采样点数。

2 系统硬件设计

系统硬件设计主要分为三大部分:DSP部分、FPGA部分、USB部分。

2.1 DSP部分设计

本系统使用的DSP芯片为TI(德州仪器)公司的TMS320VC33,它是TI公司推出的性价比极高的32位浮点型数字信号处理芯片,是目前在国内外使用最为广泛的浮点DSP之一。

TMS320VC33具有以下特点:哈佛结构;流水线操作;专用的硬件乘法器;特殊的DSP指令;快速的指令周期。另外,TMS320VC33还具有强大的浮点运算能力,运算速度可达 150MFLOPS(每秒百万次浮点运算),处理能力达到75MIPS(每秒百万次指令周期)。而且,它还采用3.3V I/O电压和1.8V处理器核电压使功耗降低到200mW。

DSP部分的电路设计主要是为TMS320VC33的外围电路设计。TMS320VC33的STRB0和引脚分别连接存储器的片选和使能引脚,实现程序/数据存储器的扩展;引脚接到高电平,INT2引脚接到低电平,实现上电后程序自加载;由TMS、TDI、TDO、TCK、、EMU0、EMU1等引脚组成程序下载口,以方便DSP程序调试。

2.2 FPGA部分设计

因为本系统的逻辑比较复杂,为了有效地减少硬件的体积、提高硬件系统的可靠性,这里把所有的逻辑控制电路、各种存储器/寄存器的地址译码电路都用一块超大规模现场可编程逻辑门阵列(FPGA)XC3090来实现。逻辑控制电路包括:命令寄存器、采样点数/采样频率设定寄存器、中断申请信号发生器、将A/D结果写入FIFO RAM的控制电路、USB及其FIFO和A/D FIFO状态检测电路。

2.3 USB部分设计

TMS320VC33与USB控制器AN2136SC之间通过双向FIFO 交换数据,握手信号使用AN2136SC的PC口。当USB为接收缓冲器时,DSP读,AN2136SC写;当USB为发送缓冲器时,DSP写,AN2136SC读。PC(0)~(3)用作二者的读写通道,方向可编程确定; PC(4)用于TMS320VC33向AN2136SC申请中断;PC(5)用于AN2136SC复位USB接收缓冲器;PC(6)用于USB接收器满标志,若接收器已满则禁止AN2136进一步对USB接收缓冲器写入;PC(7)用于USB发送缓冲器空标志,若缓冲器已空则禁止AN2136SC进一步对USB发送缓冲器读出。

3 系统软件设计

系统软件主要包括五大部分:DSP程序(用于A/D采样控制、数据处理、DSP与USB总线之间的信息交换)、USB总线驱动程序、USB固件程序(用于PC机与DSP之间的数据交换与处理)、主机应用程序、FPGA中对地址的译码程序和各个寄存器的实现程序。

1 原理概述

基于DSP和USB的高速数据采集与处理系统的原理框图如图1所示。系统上电后,DSP、FPGA分别由各自的FLASH加载程序,采集与处理系统开始运行。在A/D变换器完成转换后由FPGA向DSP发送中断0申请信号,DSP从A/D FIFO RAM中读取数据,并进行小波变换去噪处理,处理结束后DSP向USB控制器发送中断申请信号,USB控制器将处理后的数据发送至PC机,由主机应用程序显示数据。主机应用程序还可以对整个采集、处理系统进行控制,主要设定三个功能:接收处理后的数据,接收处理前的数据,设定A/D的采样频率和采样点数。

2 系统硬件设计

系统硬件设计主要分为三大部分:DSP部分、FPGA部分、USB部分。

2.1 DSP部分设计

本系统使用的DSP芯片为TI(德州仪器)公司的TMS320VC33,它是TI公司推出的性价比极高的32位浮点型数字信号处理芯片,是目前在国内外使用最为广泛的浮点DSP之一。

TMS320VC33具有以下特点:哈佛结构;流水线操作;专用的硬件乘法器;特殊的DSP指令;快速的指令周期。另外,TMS320VC33还具有强大的浮点运算能力,运算速度可达 150MFLOPS(每秒百万次浮点运算),处理能力达到75MIPS(每秒百万次指令周期)。而且,它还采用3.3V I/O电压和1.8V处理器核电压使功耗降低到200mW。

DSP部分的电路设计主要是为TMS320VC33的外围电路设计。TMS320VC33的STRB0和引脚分别连接存储器的片选和使能引脚,实现程序/数据存储器的扩展;引脚接到高电平,INT2引脚接到低电平,实现上电后程序自加载;由TMS、TDI、TDO、TCK、、EMU0、EMU1等引脚组成程序下载口,以方便DSP程序调试。

2.2 FPGA部分设计

因为本系统的逻辑比较复杂,为了有效地减少硬件的体积、提高硬件系统的可靠性,这里把所有的逻辑控制电路、各种存储器/寄存器的地址译码电路都用一块超大规模现场可编程逻辑门阵列(FPGA)XC3090来实现。逻辑控制电路包括:命令寄存器、采样点数/采样频率设定寄存器、中断申请信号发生器、将A/D结果写入FIFO RAM的控制电路、USB及其FIFO和A/D FIFO状态检测电路。

2.3 USB部分设计

TMS320VC33与USB控制器AN2136SC之间通过双向FIFO 交换数据,握手信号使用AN2136SC的PC口。当USB为接收缓冲器时,DSP读,AN2136SC写;当USB为发送缓冲器时,DSP写,AN2136SC读。PC(0)~(3)用作二者的读写通道,方向可编程确定; PC(4)用于TMS320VC33向AN2136SC申请中断;PC(5)用于AN2136SC复位USB接收缓冲器;PC(6)用于USB接收器满标志,若接收器已满则禁止AN2136进一步对USB接收缓冲器写入;PC(7)用于USB发送缓冲器空标志,若缓冲器已空则禁止AN2136SC进一步对USB发送缓冲器读出。

3 系统软件设计

系统软件主要包括五大部分:DSP程序(用于A/D采样控制、数据处理、DSP与USB总线之间的信息交换)、USB总线驱动程序、USB固件程序(用于PC机与DSP之间的数据交换与处理)、主机应用程序、FPGA中对地址的译码程序和各个寄存器的实现程序。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章