资料下载

×

高速以太网PCS子层研究及其在FPGA中的实现

消耗积分:0 |

格式:rar |

大小:4.4 MB |

2017-11-07

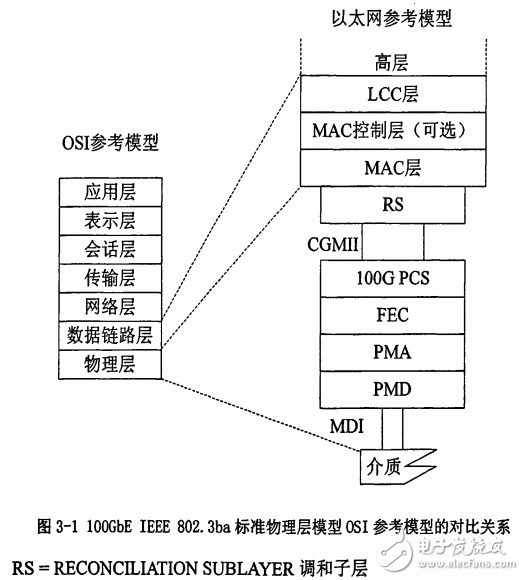

本文主要阐述内容是基于现场可编程逻辑阵列(FFGA) 对IEEE 802.3100G 以太网PCS (Physical Coding Sublayer) 子层功能的实现。首先介绍了100G 以太网相关内容,着重研究分析了100G 以太网PCS 子层功能和实现的关键技术,最后重点阐述了PCS 子层的FPGA 设计和实现、仿真及测试。引入多通道分发(MLD,Multi_lane Distribution)机制,PCS 子层把编码数据分发到多个逻辑的通道上,这些逻辑通道就称为虚通道(Virtual Lane),在目前技术和工艺条件下解决适配不同物理通道或光波长的问题,是本文设计实现的核心机制。

通过对扰码原理的分析,实现了一种任意特征多项式、任意N 位并行自同步扰码算法,并可演算得到任意特征多项式、任意N 位并行帧同步扰码算法。该方法采用递推的方法直接得出N 个时钟周期后编码器的状态值与当前编码器状态值之间的逻辑关系。其逻辑运算速度快且实现简单,十分有利于硬件实现。鉴于以上理论研究了在100G 以太网中640bits 自同步扰码算法的FPGA 实现。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(1)

发评论

-

fantasyfox

2020-12-24

0 回复 举报正在找相关资料 收起回复

fantasyfox

2020-12-24

0 回复 举报正在找相关资料 收起回复

- 相关下载

- 相关文章