资料下载

高速串行信号测试(一)

一、高速串行总线基本知识

并行总线之所以在高速传输上被串行总线取代的原因就在于:第一,系统时钟的瓶颈;第二,总线间的串扰。要达到上Gbps的传输速率,对于并行总线而言,势必时钟频率要达到GHz,就算是使用DDR方式,其系统时钟频率之高,在板级分布之困难,使得我们望而却步。而动辄几十条走线等长的排布,可控的串扰,几乎也是不可能完成的任务,而不断增加的时钟频率,又对等长走线要求越来越严格,并行总线的瓶颈似乎变得非常的突出。

串行总线没有时钟。或是说在串行总线收发两端,不需要同步时钟。这是串行总线最突出的一个特点。这是这个特点,一举将并行构架的瓶颈打破,数据速率可谓突飞猛进!最新在PC行业的动向是8Gbps的PCIEGen3。而在通信行业,超过IOGbps的串行总线早己在使用了。

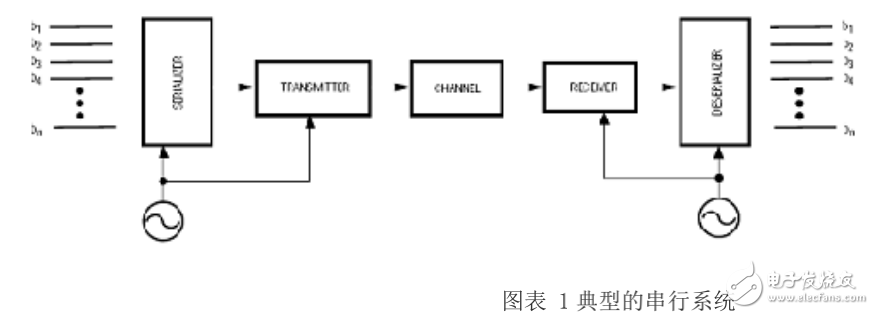

对于高速串行系统的验证与测试和传统的信号测试有自己特殊的之处,传统信号测试关心信号的模拟特征,包括时序和幅度方面特性的考察。对于并行总线而言,时序的方面的测量最主要以建立/保持时间为主,为了满足接收端能否正确的锁存数据,数据和时钟的时序必须满足建立/保持时间的要求,否则会产生误码。对于高速串行系统而言,测试的目的也是为了验证系统是否满足设计要隶的误码水平。并行和串行的差别就在于发送端和接收端对数据锁存的处理和时钟的传输上的差异。串行系统在发送断通过串行发送器将数据按照Tx clk的节拍发送到总线上,在接收端必须能够从数据中恢复出时钟,并且用该时钟锁存数据,进行解码。在串行系统中,我们不再关心时钟和数据信号之间的时序,而是关心在发送端是否能否严格按照时钟节拍发送数据;在接收端能否恢复出时钟;在互连层面关心传输线对信号完整性,特别是抖动的影响。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章