资料下载

×

如何设计实现Xilinx FPGA高速串行接口

消耗积分:0 |

格式:rar |

大小:4.30 MB |

2020-08-24

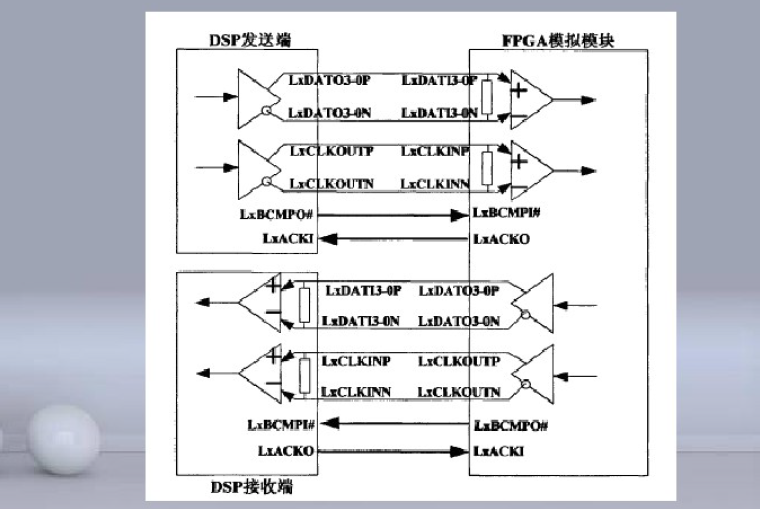

在数字系统互连设计中,高速串行/O技术取代传统的并行/O技术成为当前发展的趋势。与传统并行丨/技术相比,串行方案提供了更大的带宽、更远的距离、更低的成本和更高的扩展能力,克服了并行l/O设计存在的缺陷在实际设计应用中,采用现场可编程门阵列FPGA实现高速串行接口是一种性价比较高的技术途径。Xi的最新一代FPGA芯片 Virtex5版本,是 /irtex产品线的第五代产品,采用先进的65m三栅极氧化层工艺、新 Expressfabrie技术和 ASMBL架构Virtex.5LXT分别针对高速逻辑、数字信号处理、嵌入式处理和串行连接等应用领域进行优化。与前一代FPGA相比,Ⅵitex-5在性能和密度方面取得了巨大进步:速度平均提高30%,容量增加65%,动态功耗降低35%,静态功耗保持相同的低水平,占用面积减少45%。Ⅵitex.5LXT芯片内置了最多24个 Rocketio收发器,支持从100Mbps到3.75Gbps串行数据传输速率并支持目前流行的高速串行/O接口标准。本文从时钟、复位、电源控制发送和接收逻辑等关键方面,论述了采用vrex.5LXT芯片内的 Rocket-|Oo实现高速串行传输接口设计。基于 Xilinx ML505开发平台实现了高速串行数据传输系统,重点说明了 Rocketio特性和1.25Gbps高速串行传输的实现技术。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章