资料下载

×

基于高速CMOS时钟的数据恢复电路设计与仿真

消耗积分:2 |

格式:rar |

大小:2.35 MB |

2018-04-09

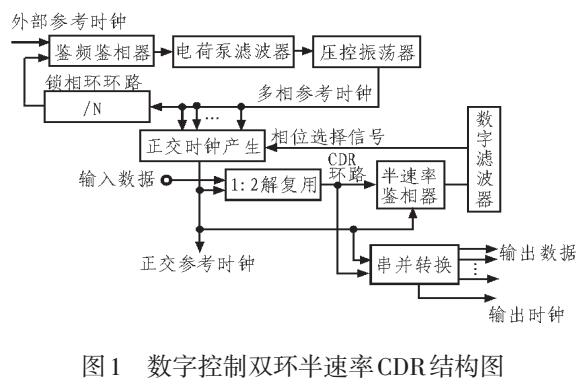

文中基于2.5 GB/s的高速型数据收发器模型,采用SMIC 0.18 um双半速率CMOS时钟进行数据的恢复处理。设计CMOS时钟主要包含:提供数据恢复所需等相位间隔参考时钟的1.25 GHz、16相频锁相环电路;采用电流逻辑模式前端电路构成的复用CDR环路;滤除亚稳态时钟的采样超前、滞后鉴相器;选择时钟与相位插值的控制时钟电路,以及基于折半、顺序查询算法的数字滤波电路。并对时钟进行数模混合仿真检测,测试结果表明:电路对于2.5 GB/s的差分输入数据,可快速高效完成数据恢复和时钟定时复位,具备极高的开发与应用前景。

下载资料需要登录,并消耗一定积分。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章