资料下载

×

用于运行AD转换器允许异步读取的μP接口的详细概述

消耗积分:0 |

格式:rar |

大小:0.08 MB |

2018-05-24

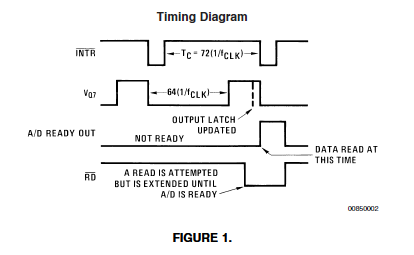

在许多数据采集应用中,必须有一个A到D转换器作为其最大转换速率工作。然后,控制微处理器将能够在软件要求的任何时间点读取最新的输入数据。为了最小化程序执行时间,数据读取可能与转换完成不同步,这存在一个问题。在A/D转换器正在更新其输出寄存器的瞬间,处理器完全可以断言读命令。所读取的数据将是转换器的输出线在从先前转换的结果到最新结果的转换中的值,并且很可能是错误的。

向A/D接口电路中添加一个简单的二进制计数器可以用来生成微处理器的就绪信号,这将防止在数据更新期间读取。图1的电路显示了一个CD4024BC7 缓冲器进位二进制计数器,它与ANADC0801、8位微处理器兼容的A到D转换器一起使用。电路操作依赖于A/D转换器的两个基本属性。首先,A/D的自由运行转换时间必须是一个恒定的时钟周期数;其次,输出锁存器必须在转换信号结束之前被更新。ADC0801满足这两个要求。在ITO低电平之前,输出数据锁存器被更新一个A/DCK周期,并且自由运行转换时间总是72个时钟周期长。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章