资料下载

TMS320x2833x和2823x直接内存存取DMA的详细用户手册免费下载

在此参考指南中描述的DMA模块是0型DMA。参见TMS320C28xx、28xxxDSP外围参考指南(SPRU566),了解具有相同类型的DMA模块的所有设备的列表、确定类型之间的差异,以及类型内特定于设备的差异的列表。

此文档使用以下约定。

●十六进制数字用后缀h或前导0x表示。例如,以下数字是40个十六进制(十进制64):40h或0x40。

本文件中的寄存器如图所示,表中描述。

每一个寄存器图形显示一个矩形,该字段被划分为表示寄存器字段的字段。每个字段都用它的位名、上面的开始和结束位号以及下面的读/写属性来标记。图例解释了用于属性的符号。

-寄存器单元中的保留位指定用于将来设备扩展的位。

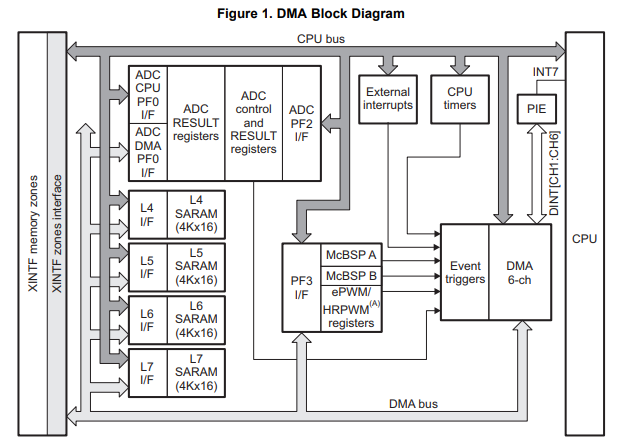

直接存储器存取(DMA)模块提供一种硬件方法,用于在外围设备和/或存储器之间传输数据,而不受CPU的干扰,从而释放带宽用于其他系统功能。此外,DMA具有在传输数据时正交地重新排列数据的能力,以及缓冲区之间的“乒乓”数据。这些特征对于将数据结构化成块以进行最佳CPU处理是有用的。

1.数字信号控制器(DSC)的强度不是纯粹以处理器速度来衡量的,而是以整个系统的能力来衡量的。作为等式的一部分,任何时候给定函数的CPU带宽可以减小,系统能力就越大。许多时候,应用程序花费大量的带宽来移动数据,无论是从片外存储器到片上存储器,还是从外围设备,如模数转换器(ADC)到RAM,甚至从一个外围设备到另一个外围设备。此外,这种数据多次出现不利于CPU的最佳处理能力的格式。本参考指南中描述的DMA模块能够释放CPU带宽,并将数据重新排列成用于更流线化处理的模式。

DMA模块是基于事件的机器,意味着它需要一个外围中断触发器来启动DMA传输。虽然可以通过将定时器配置为中断触发源来将其制成周期性的时间驱动机器,但是模块本身没有周期性地开始内存传输的机制。六个DMA信道中的每一个的中断触发源可以单独配置,并且每个信道包含它自己的独立PIE中断,以便让CPU知道DMA传输何时开始或完成。六个通道中的五个完全相同,而通道1有一个额外的特性:能够以比其他通道更高的优先级进行配置。DMA的核心是状态机和紧密耦合的地址控制逻辑。正是这种地址控制逻辑允许在传输期间重新排列数据块以及在缓冲区之间进行乒乓数据的处理。这些特性中的每一个以及其他将在本文档中详细讨论。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章