资料下载

×

如何使用FPGA设计SDH的设备时钟详细原理和测试资料概述

消耗积分:0 |

格式:rar |

大小:0.74 MB |

2018-11-02

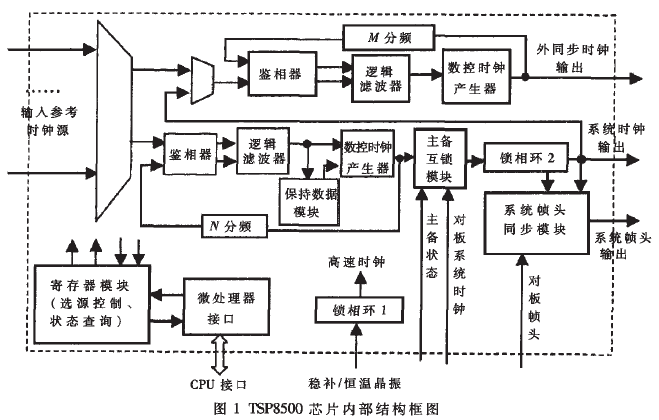

介绍了一种采用FPGA 设计的SDH 设备时钟的构成及设计原理; 并给出了相关的测试结果; 测试结果表明该SDH 设备时钟完全满足ITU- T G.813 建议规范的各项时钟指标要求。

SDH 设备时钟(SEC)是SDH 光传输系统的重要组成部分, 是SDH 设备构建同步网的基础, 也是同步数字体系(SDH)可靠工作的前提。SEC 的核心部件由锁相环构成。网元通过锁相环跟踪同步定时基准, 并通过锁相环的滤波特性对基准时钟在传输过程中产生的抖动和漂移进行过滤。而当基准源不可用时, 则由SEC 提供本地的定时基准信息, 实现高质量的时钟输出。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章