资料下载

如何使用FPGA设计高速实时数据采集存储系统的资料概述

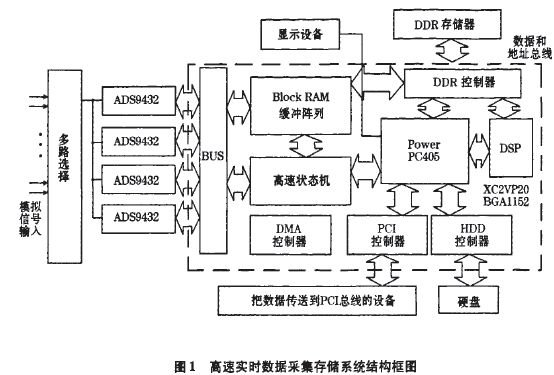

设计了以FPGA器件XCSVIXS0为核心处理芯片的高速数据采集存储系统。在XCSVLXS0内部实现的高速状态机和相位延迟时钟作用下,采用4片高速A/D器件流水工作来提高数据采集速度。同时在XCSVLXS0内实现的FLASHMEMORY控制器的作用下,实现了数据在存储器阵列的高速存储,数据采集系统可实现百兆以上速度的实时采集存储。

在传统的数据采集系统中,A/D的控制和数据的转存均通过CPU或者MCU来完成。在这种方式下,将A/D转换的结果读人,然后再转存到片外的存储器中,这一过程至少需要4个机器周期。即使对于ARM芯核的单片机(CPU采用流水线结构,1个机器周期占1个CLK),使用33 MHz的晶振,它的最高转存数据速度也只达到8 Mbit/s.在高速采样系统中,这种方式一方面占用太多CPU资源,另外也远远不能满足高速采样的速度要求。同时,在数据采集系统的前端数字信号处理(DSP)中,如FFr、FIR、IIR滤波等,以往一般都是利用DSP内部的硬件乘法器加软件控制来实现。DSP的工作方式是通过内部的CPU逐条执行软件指令来完成各种运算和逻辑功能的,在排队式串行指令执行方式下,工作速度和效率也将降低。为了提高数字信号处理速度,现在一些实现专用算法的DSP模块和通信接口也由FPGA或者CPLD实现。基于上述原因,设计了以Viaex一5系列的XCSVIXS0为核心处理芯片的多路数据采集系统,它以硬件电路方式来提高速度。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章