资料下载

如何使用Synopsys PAC进行标准单元布局的改进

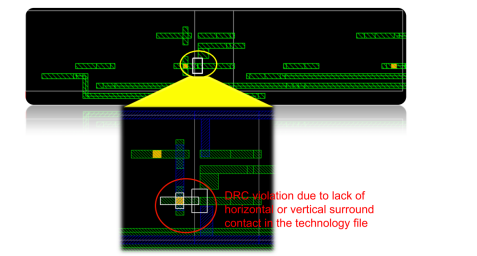

虽然标准单元布局是用最小设计规则绘制的,以最大限度地提高设计区域收缩的效益,但复杂的设计规则给信号路由访问标准单元布局中的管脚带来了困难。因此,对于物理布局设计师来说,设计一个针对面积、功率、时间、信号完整性和可打印性进行优化的标准单元布局已经成为一个巨大的挑战。在标准单元布局期间,需要多次设计迭代来考虑插针可访问性,以增加路由器可用的可行解决方案的数量。在这项工作中,我们将演示Synopsys PAC方法的几个改进,例如在相同的细胞基台条件下减少每个Synopsys“测试细胞”所需的细胞数量,增加插针连接的复杂性,以更好地评估插针的可及性。我们还建议附加约束以提高检测插针可访问性问题的可能性。我们还集成了其他物理验证方法来访问标准单元的设计规则遵从性和可打印性。我们希望易于使用的实用程序能够使布局工程师执行验证,简化验证方法。

CMOS技术的不断扩展现在正面临着使用193i光刻工艺的瓶颈。与图案相关的缺陷继续增加,并限制了每片晶片的良好模具数量。传统的基于规则的设计规则检查(DRC)方法不再足以保证100%的模式可打印性。从全球铸造40纳米技术开始,需要设计可制造性(DFM)验证来识别制造弱点,并防止诸如开(缩颈)和短路(桥接)等灾难性错误,从而使早期斜坡获得良好的产量。

随着每一代新技术中物理验证的增加,知识产权(IP)库的开发资源变得极具挑战性和成本高昂。特别地,标准单元IP库是构建位置和路由(P&R)数字电路设计的首要和最重要的设计基础库;标准单元布局的质量直接影响芯片设计的面积和可制造性。今天,我们观察到限制标准单元库质量的主要挑战是分别放置针位置和光刻兼容(光刻可打印性和颜色兼容)设计。因此,需要对电路设计所施加的设计限制进行早期评估。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章