资料下载

如何使用X-DSP可测性设计与片上调试技术的研究与实现

随着芯片规模的增大和复杂度的上升,片内信号的观测和控制更加困难,对芯片的测试及调试的难度也在不断上升,芯片的测试和调试问题成为制约整个行业发展的重要因素。如何合理地对数字信号处理器进行可测性设计、建立调试支持成为数字信号处理器设计的核心问题之一。

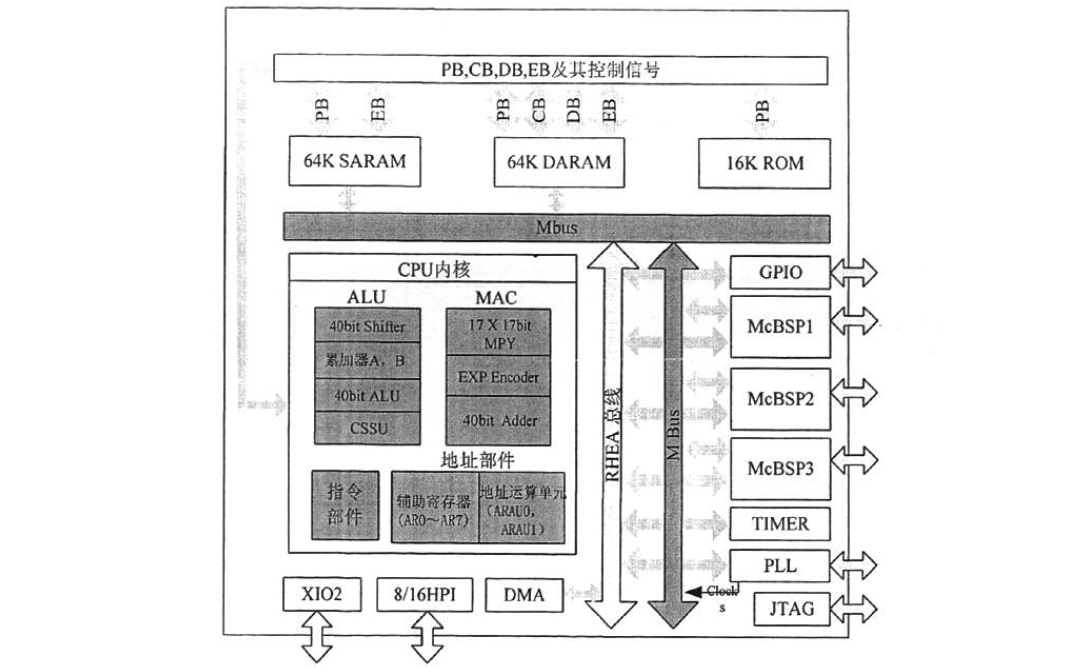

X—DSP是作者参与研制的一款高性能低功耗DSP。它具有高级的改进哈佛结构,带有专用逻辑功能的CPU,片内存储器,片内外设和高度专业化的指令集。

本文根据X.DSP的体系结构特点及X.DSP对测试的具体需求,提出并实现了包含边界扫描设计和内部全扫描测试技术在内的一整套可测性设计方案。该方案充分考虑了X.DSP的内部结构,以IEEEl 149.1标准为基础,有针对性的选择了一系列成熟可靠的可测性技术和方法,充分利用X.DSP所具有的处理能力和CPU特有的地址、数据总线结构,在尽量少的增加测试开销的前提下很好的满足了X.DSP对测试的需求。本方案采用自主设计扫描单元的方法实现,大大的提高了设计的灵活性,为调试与测试的接口整合提供了支持。

本文深入研究了X.DSP在系统级、指令级、硬件结构级等不同层次上对调试的需求,在上述测试结构的基础上设计了简洁高效的片上硬件调试结构,以很少的调试硬件代价提供了很强的调试能力,通过扫描链结构实现了高效的调试通信和控制通路,支持硬件设计人员对X.DSP内部状态的控制和观察以及对用户程序的调试分析,很好的满足了X.DSP不同层次的调试需求。

同时本文将调试结构、内部扫描和边界扫描集成在一起,使其共用测试引脚,降低了囡测试而带来的芯片引脚开销。

为了保证设计的正确性,本文最后对该结构进行了较为完备的测试码开发和功能验证,验证结果表明本文实现的测试与片上调试逻辑运行正确。该结构已经在投片后的X-DSP芯片中得到了实际应用。在投片后的验证过程中,该结构配合X.DSP的集成开发环境,可以实现用户程序的加载、运行、调试和分析。板级调试的实际结果表明,该结构能够正确运行。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章