资料下载

×

ICS854105AGLFT LVCMOS LVTTL到LVDS时钟扇出缓冲区的数据手册

消耗积分:2 |

格式:pdf |

大小:0.21 MB |

2019-07-22

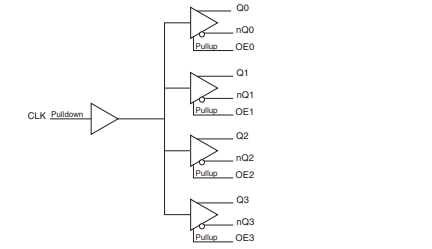

854105是一种低歪斜、高性能的1到4 LVCMOS/LVTTL到LVDS时钟扇出缓冲区。利用低压差分信号(LVDS),854105提供了一种低功耗、低噪声的解决方案,用于将时钟信号分布在100Ω的受控阻抗上。854105接受LVCMOS/LVTTL输入电平,并将其转换为LVDS输出电平。

有保证的输出和部分到部分的倾斜特性使854105非常适合那些需要明确定义的性能和可重复性的应用。

特征

•四个差分LVDS输出对

•一个单端LVCMOS/LVTTL输入

•CLK可接受以下输入电平:LVCMOS、LVTTL

•最大输出频率:250MHz

•将单端输入信号转换为LVDS电平

•附加相位抖动,rms:0.16ps(典型)

•输出偏差:55ps(最大)

•部分到部分倾斜:350ps(最大)

•传播延迟:1.62ns(最大)

•3.3V工作电源

•0°C至70°C环境工作温度

•无铅(RoHS 6)包装

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章