RDMA高性能实践之软硬件融合设计思路

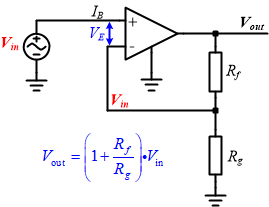

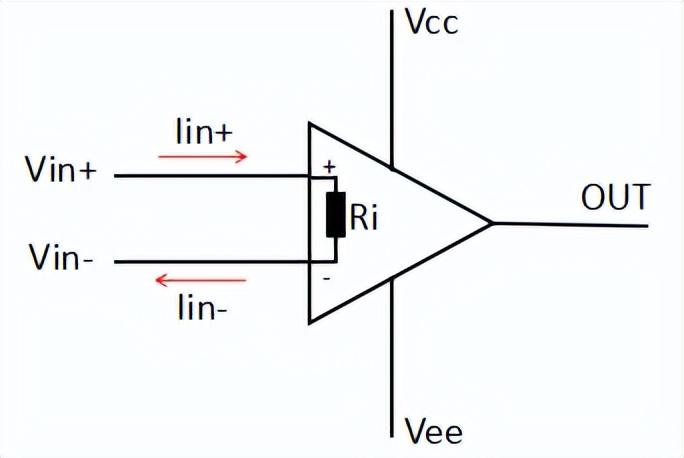

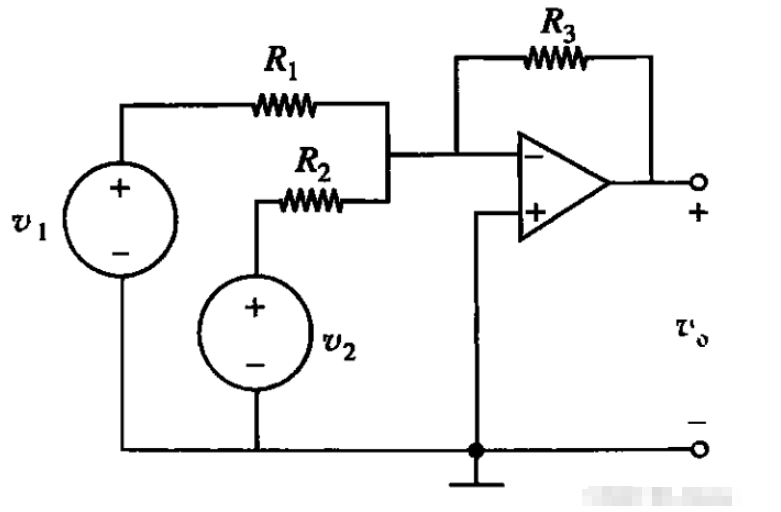

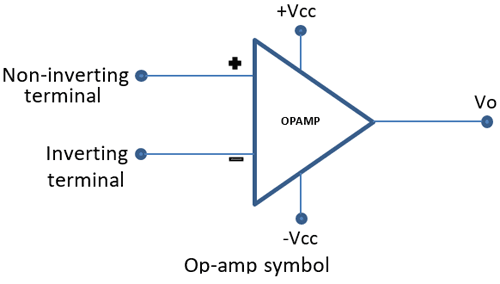

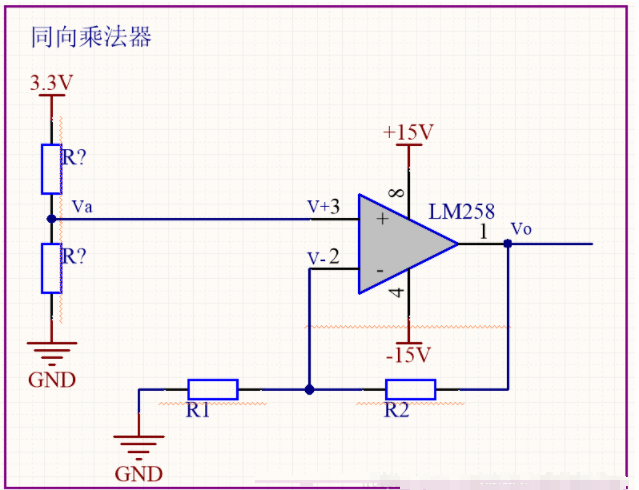

四种基本的运算放大电路详解

运算放大器的常用电路图及其工作原理

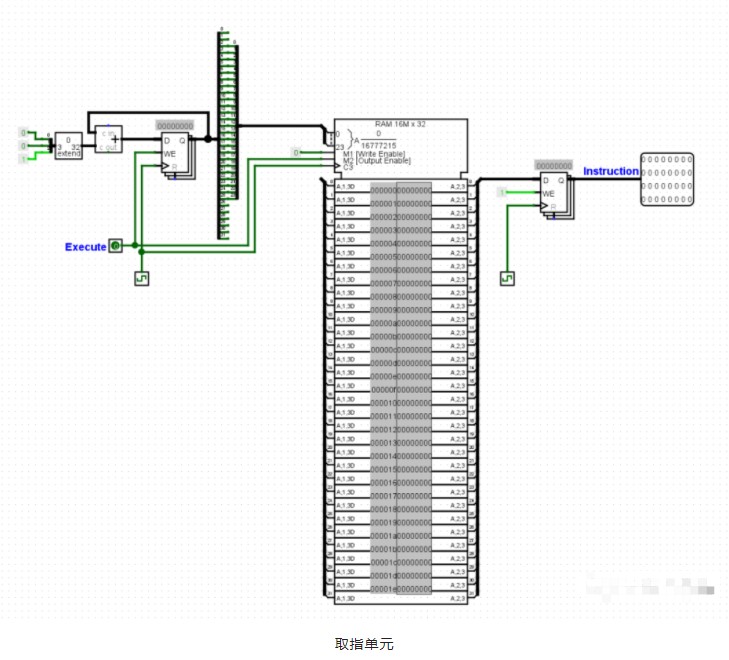

剖析一下CPU对代码的识别和读取

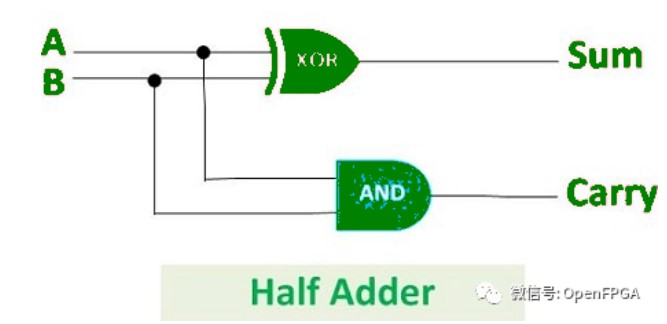

FPGA的算法解析1:整数操作与加减法器

基本运算电路分享

FPGA技术的流水线设计思想解析

如何使用LM358运算放大器来演示加法器电路

怎样测量加法器的速度?器件延迟的时间长度!

使用Verilog硬件描述语言练习加法器设计

运算放大器电路分析方法

CPU整体框架是由哪几部分组成的

超前进位加法器是如何实现记忆的呢

三种高速乘法器实现原理

如何用小脚丫FPGA核心板实现4位加法器功能

加法器是如何实现的

基于Verilog硬件描述语言实现SHA-1算法的设计

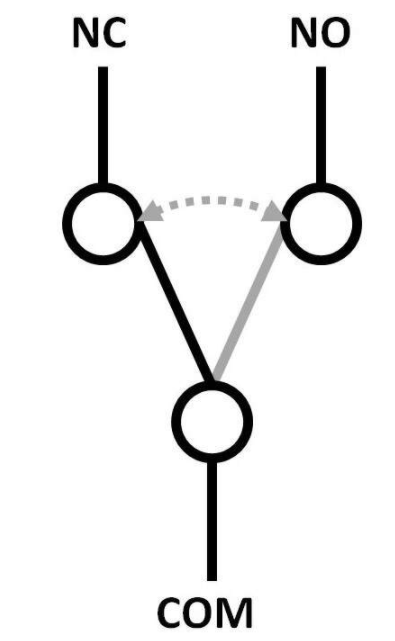

基于“ Y”开关的概念来构建中继计算机

一种很简单的增量调制(DM)编码

基于AXI总线的加法器模块解决方案