Verilog逻辑设计中的循环语句和运算符

Verilog HDL中常用预编译命令介绍

Verilog时序逻辑中同步计数器的功能和应用

Verilog设计中函数和任务的作用分析

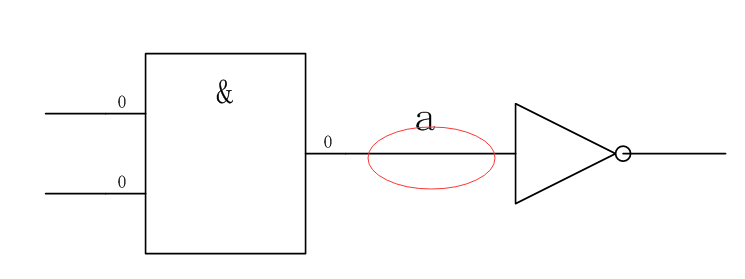

Verilog进行组合逻辑设计时的注意事项

如何用小脚丫FPGA核心板实现4位加法器功能

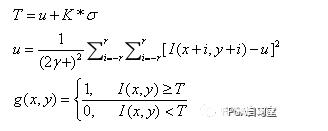

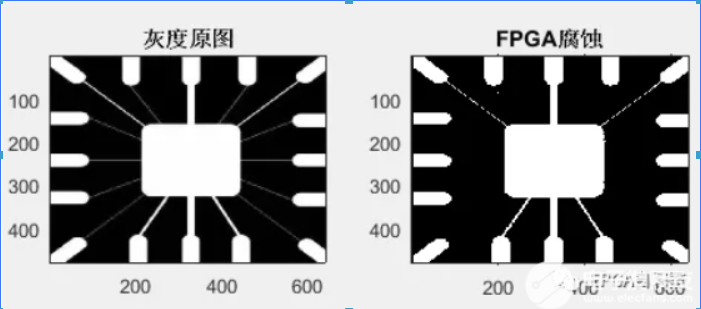

基于FPGA的自适应阈值分割算法实现

基于Verilog的“自适应”形态学滤波算法实现

Verilog语言中阻塞和非阻塞赋值的不同

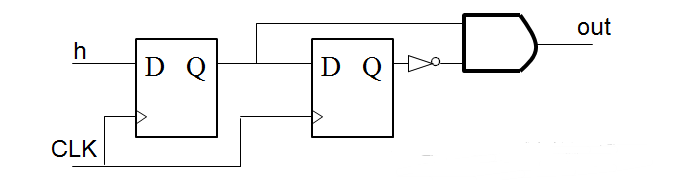

浅谈Verilog复杂时序逻辑电路设计实践

加法器是如何实现的

【ZYNQ Ultrascale+ MPSOC FPGA教程】第三章Verilog基础模块介绍

FPGA的入门基础知识详细说明

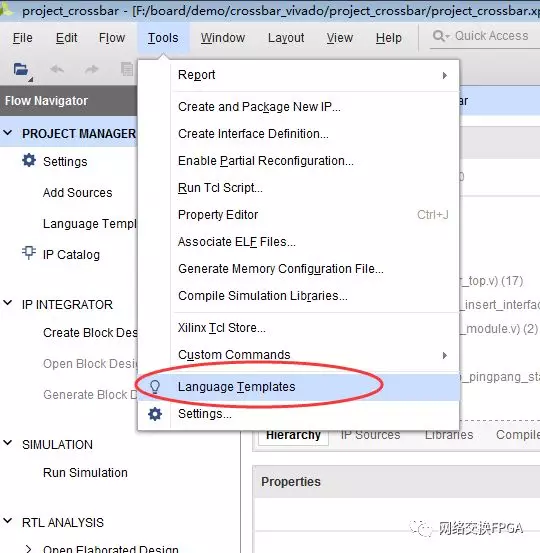

如何快速在Verilog和VHDL之间互转

Verilog设计增加延时的仿真技术

基于共享缓存的架构的系统“假性卡死”问题分析

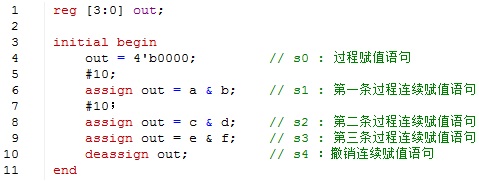

Verilog中的赋值语句的区别

基于FPGA的Verilog实现VGA驱动电路

关于verilog中的无符号数和有符号数

FPGA工程的Verilog HDL初学者设计要点