基于VIVADO搭建ARM+FPGA系统架构实现软硬件联合开发

基于AXI总线的加法器模块解决方案

探索Vivado HLS设计流,Vivado HLS高层次综合设计

PYNQ设计案例:基于HDL语言+Vivado的自定义IP核创建

错误时钟偏移计算导致错误时序收敛的解决方案

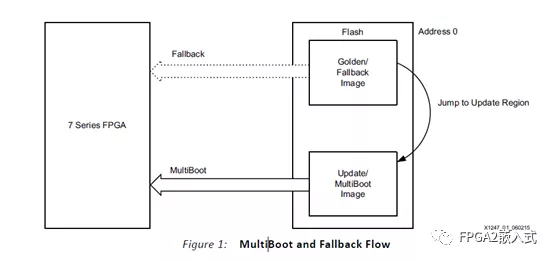

7 eries FPGAs SPI MultiBoot实现方式

浅析可提升Vivado编译效率的增量编译方法

基于PFGA的脱离Vivado单独建仿真环境工程

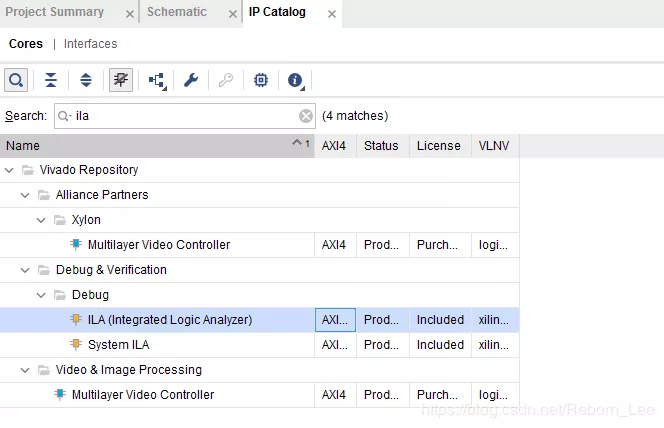

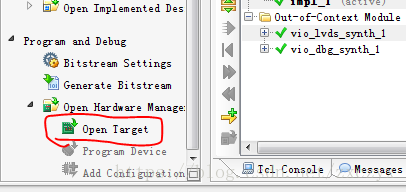

关于Vivado中三种操作Debug的方式

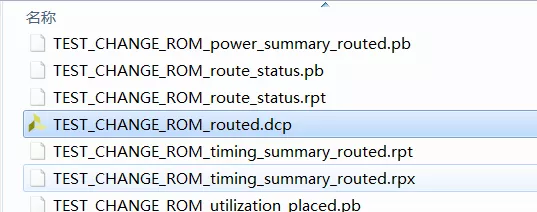

修改BRAM初始化值的避免综合与实现

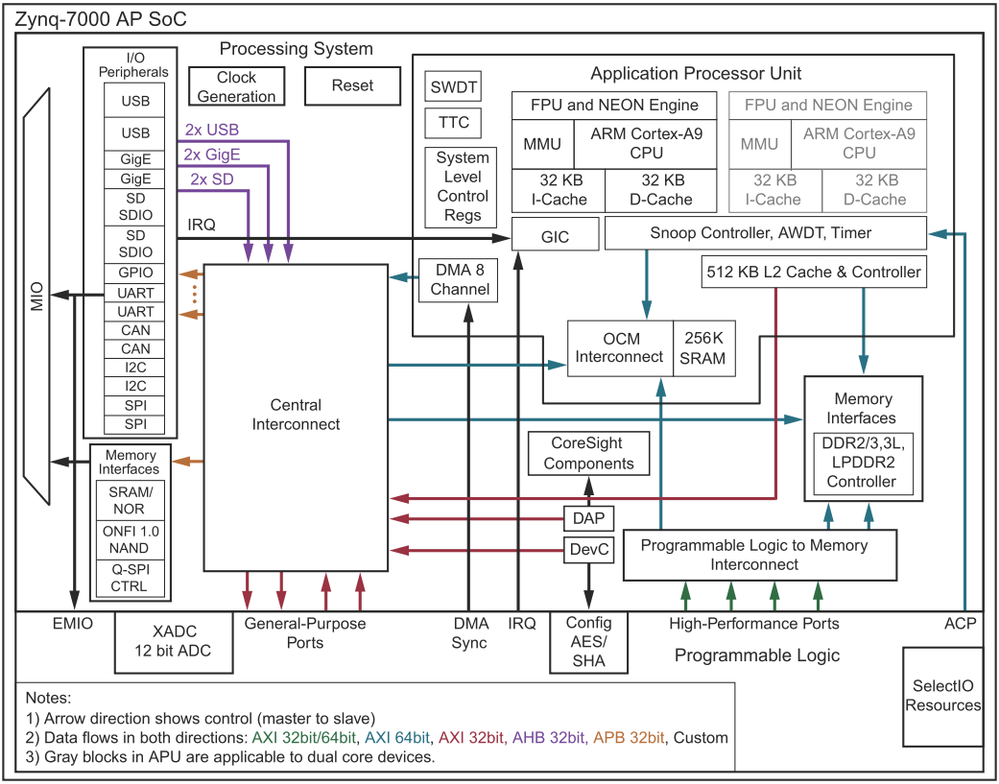

Vivado中进行ZYNQ硬件部分设计方案

vivado约束案例:跨时钟域路径分析报告

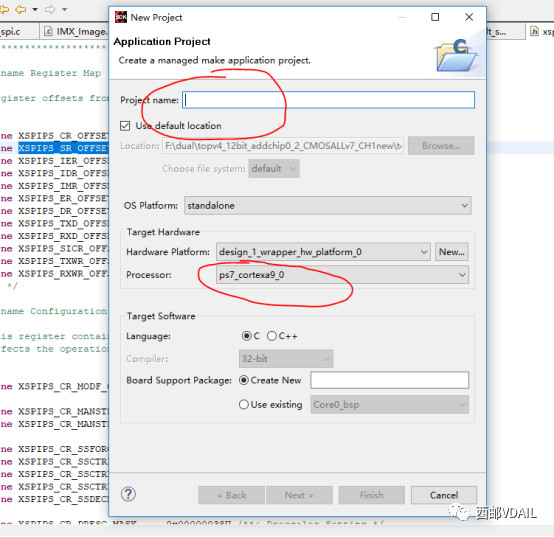

生成zynq裸核启动文件步骤解析

【vivado学习】典型时序模型的三条时钟路径分析

详细解析vivado约束时序路径分析问题

xilinx FPGA中oddr,idelay的用法详解

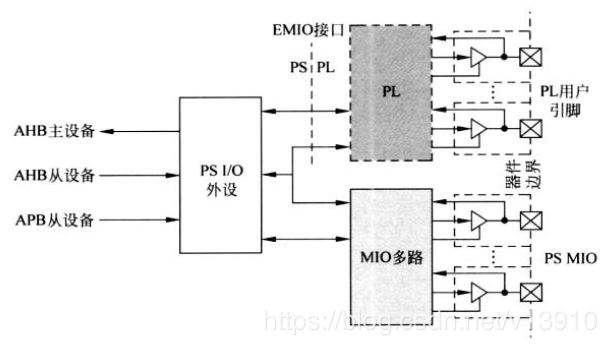

MIO与EMIO的关系解析 GPIO、MIO、EMIO的区别

Xilinx FPGA案例学习之Vivado设计综合约束

如何擦除固化在FPGA的程序

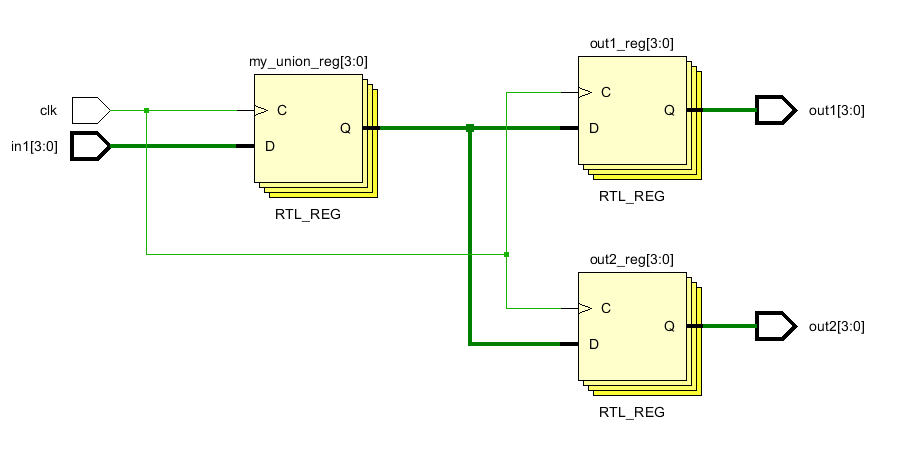

SystemVerilog 中各种不同的联合解析