XCVU27P-3E和 XCVU29P-3E的速度文件参数已更新

在PL设计中使用MPSoC EMIO GPIO

如何在Vivado Design Suite中完成平台准备工作

Vivado仿真器中的通用验证方法学(UVM)支持

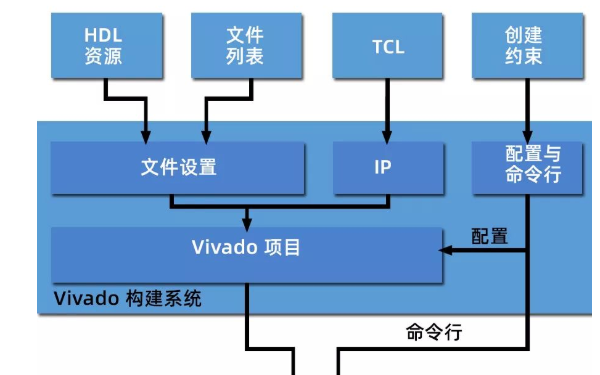

FPGA构建环境的自动化怎么实现

Vivado调试ILA debug结果也许不对

多重驱动是什么?为什么需要解决

Vivado进行时序约束的两种方式

XDC时钟约束的三种基本语法

Xilinx Vitis统一软件平台面向所有开发者解锁全新设计体验

将自定义IP内核添加到Vivado中

Vivado综合引擎的增量综合流程

赛灵思器件和工具支持多种数据类型同时满足设计性能目标要求

Vivado 专家系列演讲

软件更新:Vivado 2019.1 现已开放下载

Vivado

改Vivado运行几个内核

关于Vivado时序分析介绍以及应用

Xilinx发布唯一SoC增强型Vivado设计套件,可大大提高生产力

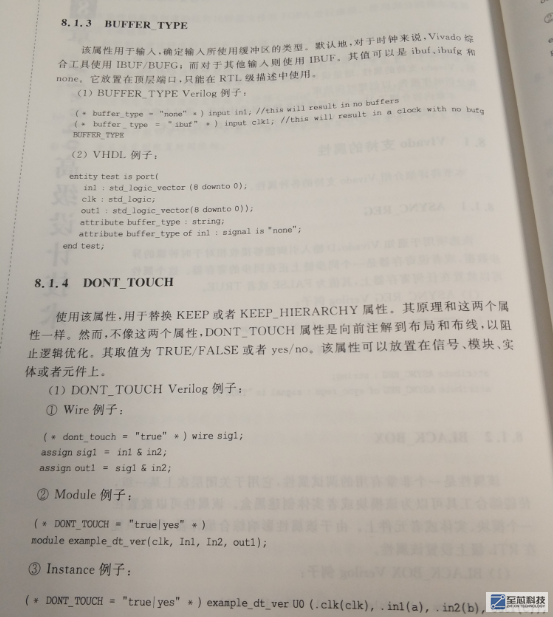

Vivado防止信号被综合掉的三种方法