资料下载

×

如何实现频率合成器的高性能架构

消耗积分:1 |

格式:pdf |

大小:0.44 MB |

2020-07-07

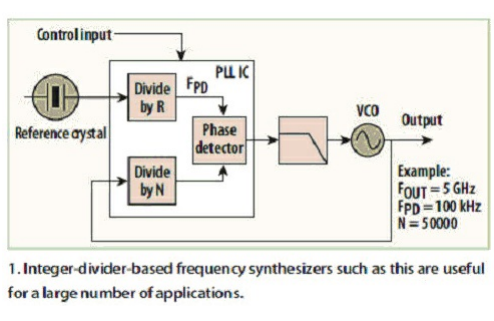

要满足苛刻的频率合成器要求,通常需要做到一定程度的设计灵活性。基本的锁相环(PLL)频率合成器能以低成本、高空间效率、低功耗封装提供合理的频谱纯度和频率捷变,因此它在射频(RF)系统核心位置发挥作用已经有段时间了。但是,在要求快速切换速度、低相位噪声或低杂散信号电平的场合,有必要使用更为复杂的架构。通过正确的设计方法,结合使用现代低成本高集成度的PLL和直接数字合成器(DDS)集成电路(IC)可以极大地促进高性能架构的实现。大部分高频系统都使用传统的基于整数分频器的设计(图1)或基于分数N分频器的设计。不管是使用哪种设计,联合使用单个通用频率合成器IC和一个外部压控振荡器(VCO)通常都可以实现要求的功能。VCO功能可以用IC、模块或分立元件解决方案甚至在合成器芯片内部实现,具体取决于所要求的频率范围、相位噪声性能以及空间、成本和功耗约束条件。最终设计通常以制造商的应用笔记为基础,并且一般可以使用可下载的应用程序完成合成器的寄存器加载和相位检测器增益的设置等功能。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章