资料下载

驱动高压锁相环频率合成器电路中的VCO详细分析

锁相环(PLL)电路是由压控振荡器(VCO)和鉴相器组成的反馈系统,振荡器信号跟踪施加的频率或相位调制信号是否具有正确的频率和相位。需要从固定低频率信号生成稳定的高输出频率时,或者需要频率快速变化时,都可以使用PLL。典型应用包括采用高频率、电信和测量技术实现滤波、调制和解调,以及实现频率合成。

图1所示为基于PLL的频率合成器框图。VCO生成输出信号。通过PLL将其保持在设定频率,并锁定到基准频率。基准频率通常由非常精准的石英振荡器提供。在锁相环电路的反馈路径部分,在鉴相器前通过分频器提供可调的VCO分频比。

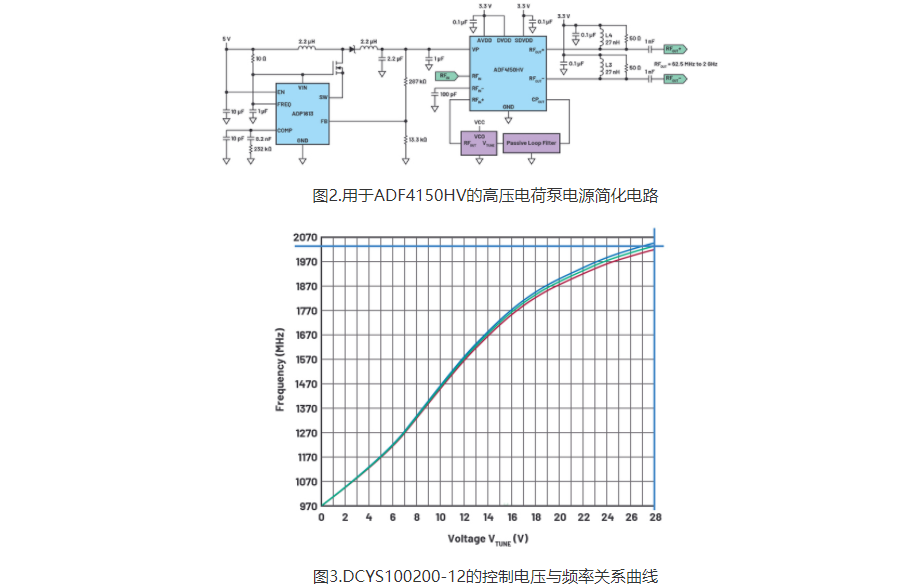

VCO包含可调的调谐元件,例如电容随输入电压改变的变容二极管。因此,PLL电路可以算一种VCO反馈控制系统。VCO所需的输入或控制电压通常高于提供给PLL电路的电源电压。电源电压一般为3.3 V或5 V,而VCO根据频率需求可能需要高于20 V的电压。要生成范围更广泛的频率,可以使用具备更广泛调谐范围的VCO。图2显示了支持千兆赫范围VCO的简单电路示例。

VCO可以使用Synergy Microwave Corporation的DCYS100200-12。该产品在28 V (VTUNE)时产生2 GHz频率,如图3所示。

生成高控制电压,有几种可行方案。其一是使用有源环路滤波器,该滤波器基本是由高速放大器和低通滤波器构成,可以将来自鉴相器(CPOUT)的输出脉冲转化为干净的直流电压。或者,可以使用带集成电荷泵的PLL频率合成器,例如ADI的ADF4150HV,该器件不需要额外的有源环路滤波器。虽然这两种解决方案都需要高压电源,但是使用ADF4150HV可以减少所需的组件数量。也可以避免有源滤波放大器导致的失真和相位噪声。此外,ADF4150HV允许实现小数N或整数N锁相环频率合成器。最终VCO的频率可以进行1、2、4、8或16分频,使得输出频率最低可达到31.25 MHz。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章