资料下载

×

Verilog中经常会使用那些基础知识详细资料说明

消耗积分:0 |

格式:docx |

大小:0.02 MB |

2019-08-30

Verilog中常用到的基础知识

一、Assign(连续赋值语句):对信号的命名或定义。

二、N’bxxxxx:N代表几根线,b是二进制(八进制o,十进制d,十六进制h)

三、Wire、parameter和reg:定义信号,在always模块里只能用reg定义,其他的如assign、例化模块的输出信号用wire。Parameter用于定义常数。

Wire用于连续赋值语句,reg用于过程赋值语句,输入输出端用wire赋值(直通的,输入值变化、输出也跟着立刻变化),寄存器用reg赋值(需要触发才能进行相应语句的执行)。

四、位选、reg[2:0]a表示a有三根线 reg[n:0]a表示a有n跟线

A[n]表示a的第n跟线

data[cnt]《=0:将0赋值给data中的第cnt跟线

五、data《=din[cnt]:将din中的第cnt跟线的值赋值给data

六、位拼接:data《={data[n-1:0],data[n]} data[n:0]《= {data[n-1:0],data[n]}

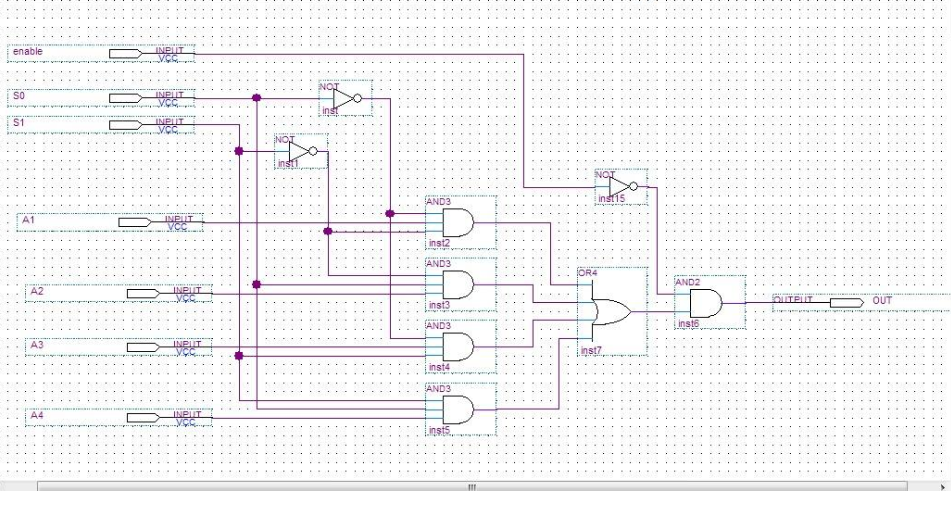

七、例化:就是将模块与模块之间连接起来

Always语句块:构成时序电路的关键词, always语句由于其不断重复执行的特性,只有和一定的时序控制结合在一起才有用

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章