资料下载

FPGA的配置引脚说明

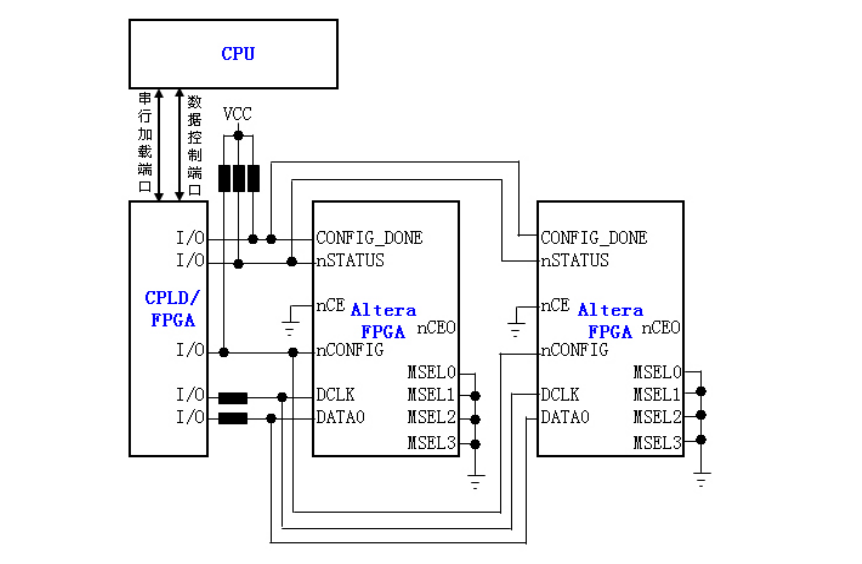

FPGA是基于SRAM编程的,编程信息在系统掉电时会丢失,每次上电时,都需要从器件外部的FLASH或EEPROM中存储的编程数据重现写入内部的SRAM中。FPGA在线加载需要有CPU的帮助,并且在加载前CPU已经启动并工作。FPGA的加载模式主要有以下几种:

1).PS模式(Passive Serial Configuration Mode),即被动串行加载模式。PS模式适合于逻辑规模小,对加载速度要求不高的FPGA加载场合。在此模式下,加载所需的配置时钟信号CCLK由FPGA外部时钟源或外部控制信号提供。另外,PS加载模式需要外部微控制器的支持。

2).AS模式(Active Serial Configuration Mode),即主动串行加载模式。在AS模式下,FPGA主动从外部存储设备中读取逻辑信息来为自己进行配置,此模式的配置时钟信号CCLK由FPGA内部提供。

3).PP模式(Passive Parallel Configuration Mode),即被动并行加载模式。此模式适合于逻辑规模较大,对加载速度要求较高的FPGA加载场合。PP模式下,外部设备通过8bit并行数据线对FPGA进行逻辑加载,CCLK信号由外部提供。

4).BS模式(Boundary Scan Configuration Mode),即边界扫描加载模式。也就是我们通常所说的JTAG加载模式。所有的FPGA芯片都有三个或四个加载模式配置管脚,通过配置MESL[0..3]来选取不同的加载模式。首先来介绍下PS加载模式,各个厂商FPGA产品的PS加载端口定义存在一些差异,下面就对目前主流的三个FPGA厂商Altera,

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章