资料下载

使用FPGA实现直流伺服电机控制器的设计资料说明

直流伺服电机处理器,如单片机、DSP 具有产生 PWM 信号和捕获电机编码器信号的能力,但对 IC 产生 PWM 信号的通道数目和电机编码器捕获通道数目有限。对多个直流电机的伺服控制很难满足要求。故设计基于 FPGA 直流伺服电机控制器。

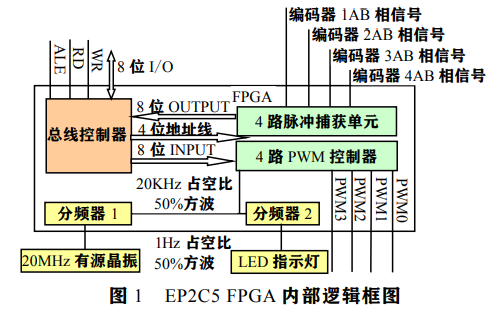

在 Cyclone EP2C5T FPGA 内部设计各 4 路 PWM 发生器和编码器脉冲捕获单元。其 PWM 信号通道和编码器脉冲捕获单元数目可基于 VHDL 硬件描述语言按需调整。如图 1,包括总线和 4 路 PWM 控制器、4 路脉冲捕获单元、分频器 1,分频器 2。总线控制器根据 WR、RD、ALE 信号完成 FPGA 内部地址锁存及 8 位 OUTPUT 总线、8 位 INPUT 总线的控制。FPGA 外接 20 MHz 有源晶振,时钟信号经分频器 1 分频后得到 20 kHz 占空比为 50% 的方波信号。4 路 PWM 控制器以该信号为基准,产生频率为 20 kHz,占空比可调的 4 路 PWM 信号。4 路 PWM 信号可依 4 位地址线独立控制。4 路脉冲捕获单元用于对电机编码器脉冲信号进行捕获。通过总线控制器将脉冲捕获值读出到 8 位 I/O 口上。分频器 2 将 20 kHz 方波信号 20000 分频得到 1Hz 占空比为 50 %的方波信号,直接驱动 LED 灯,指示系统状态。EP2C5 FPGA 内部逻辑在 Quartus II 6.0 环境下使用 VHDL 硬件描述语言实现。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章