资料下载

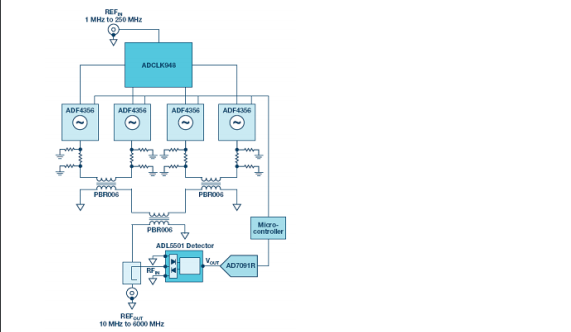

如何使用宽带频率合成器件实现相位校准的控制

顾名思义,锁相环(PLL)使用鉴相器比较反馈信号与参考信号,将两个信号的相位锁定在一起。虽然这种特性有许多用武之地,但是PLL如今最常用于频率合成,通常充当上变频器/下变频器中的本振(LO),或者充当高速模数转换器(ADC)或数模转换器(DAC)的时钟。直到最近,我们很少注意这些电路中的相位行为。但随着对效率、带宽和性能的需求日益增长,RF工程师必须推出新技术来提高频谱和功率效率。信号相位的重复性、可预测性和可调性在现代通信和仪器仪表应用中均起到日益重要的作用。

一切都是相对的

关于相位测量,如果不是相对于另一个信号或相对于原始相位则毫无意义。例如,使用矢量网络分析仪(VNA)对放大器之类的两端口网络进行相位测量,就是相对于输入相位ANG(S21)测量输出相位的。单输入相位指相对于入射相位ANG(S11)的反射相位。在PLL合成器上,相位测量指的是相对于输入参考相位的测量或信号间的相位测量。任何相位测量的理想状态就是测得与原始相位相比的精确期望值,但是非线性、非理想性、温差和电路板迹线以及其他制造差异都会使得相位在信号生成中更容易发生改变。对于本文而言,“同相”是指幅度和时序特性相同的信号;确定性相位是指信号之间的相移是已知和可预测的。

示波器测量相位

为了比较两个不同频率的相位,可以使用高速示波器比较输出相位与参考相位,这是一种相对直观的方法。为了直观可见,输入相位和输出相位通常必须是彼此的整数倍。这在许多时钟电路中相对比较常见。对于整数N分频PLL,输入频率(REFIN)和输出频率(RFOUT)之间的关系通常是确定和可重复的。只需将示波器探头放在REFIN和RFOUT上,但注意仅捕获确定已建立相位时的信号。像RTO1044这样的高级示波器,只有在满足某些条件时才允许事件触发激活:比如将特定的数字模式写入 PLL器件以及已知信号的上升沿出现时。鉴于数字模式的写入与最终信号稳定之间可能会有一些延迟,因此在这两个事件之间插入一些延迟至关重要,这种特定型号的仪器就可以实现这一功能。图1的测量是为了确认ADF4356 PLL相对于已知参考信号(在这种情况下,另一个ADF4356设定相同的输出频率)的相位延迟在上电时是否恒定和可重复。为了正确设置仪器,将两个低速探头连接到ADF4356 SPI接口的CLK线路和DATA线路。若要将数字模式写入特定频率,则必须等待1秒钟,仪器才能捕获显示两个PLL输出的时域图。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章