资料下载

×

FPGA时序约束的常用指令与流程详细说明

消耗积分:0 |

格式:rar |

大小:0.89 MB |

2021-01-11

约束流程

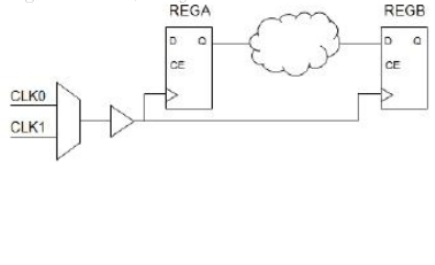

说到FPGA时序约束的流程,不同的公司可能有些不一样。反正条条大路通罗马,找到一种适合自己的就行了。从系统上来看,同步时序约束可以分为系统同步与源同步两大类。简单点来说,系统同步是指FPGA与外部器件共用外部时钟;源同步(SDR,DDR)即时钟与数据一起从上游器件发送过来的情况。在设计当中,我们遇到的绝大部分都是针对源同步的时序约束问题。所以下文讲述的主要是针对源同步的时序约束。

根据网络上收集的资料以及结合自己的使用习惯,我比较趋向于下面的约束流程方式:时序约束一共包含以下几个步骤:时钟约束、IO约束以及时序例外。这几个步骤应该可以解决我们设计当中绝大多数情况下的时序约束问题。

1.首先约束时钟。输入时钟,输出时钟。从种类 来看不外乎以下几种:单端输入时钟、差分输入时钟、GT或恢复时钟(例如LVDS信号恢复出来的时钟)、PLL产生的时钟以及自己产生的门控时钟。

2.IO约束。只有等待内部时钟完全通过后,再配置input delay和output delays,告知FPGA外部端口的数据时序关系。

3.时序例外。在约束完时钟以及IO后,还是有时序违例的时候,注意检查一下是否有时序例外的情况,例如多周期时钟路径、异步时钟、常量、以及互斥时钟路径等等。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章