资料下载

Intel FPGA时序约束的基础概念详细说明

一、引言

由于每次我都写了功能仿真过后,放到门级仿真,就出问题,而门级仿真通常对实际还是有一定的指导意义的,通常我只要门级仿真跑不出来,多半实际都没跑出来,而且门级仿真调试起来相当麻烦,所以功能仿真+时序约束+signal tap 才是最好的方法。

之前花了2个星期看了某金的静态时序分析,收货甚微,发现里面的话自己都扯不转,动不动就用粗话来解释,实在一点也不严谨,一点也不学术,对于一个追求转行的人来说,实在看不下去,浪费了我2星期,实在生气。时隔4个月,再次决定自己从官方下手,来逐渐完善时序约束,只要intel的time quest学会了,那Vivado的时序约束自然不在话下了。另外,在以后的面试中,时序约束也是一很重要的部分,决不能马马虎虎,大概了解即可的态度。另外,一定要耐心的阅读,仔细的思考,你可以看看官方文档(文档连接在下方有连接)结合我的理解一起学习,我的理解不一定完全正确,欢迎指点批评。官方的公式提供了很多,但是实际上,我们不需要记住这些这么多的公式,看看就好,在本文,我总结了需要记住理解的公式(工程不需要,time quest会自动计算出),但是面试很可能问到。

二、时序术语terminogy

1、数字电路原理

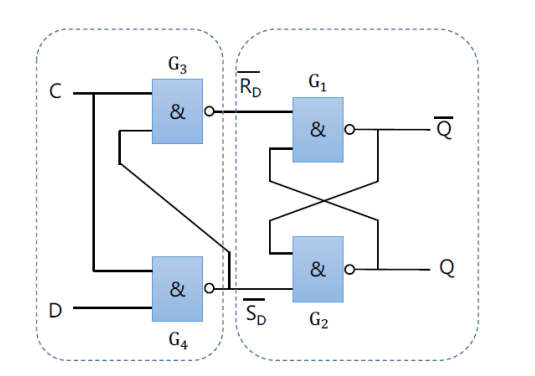

1.1、D锁存器:

能够将输入端的单路数据D存入到锁存器中的电路,此时寄存器的状态是由激励输入端D来确定的,并且D等于什么,寄存器的状态就是什么,也就是说,将单路数据D存入到了锁存器中。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章