资料下载

FPGA时序约束的理论基础知识说明

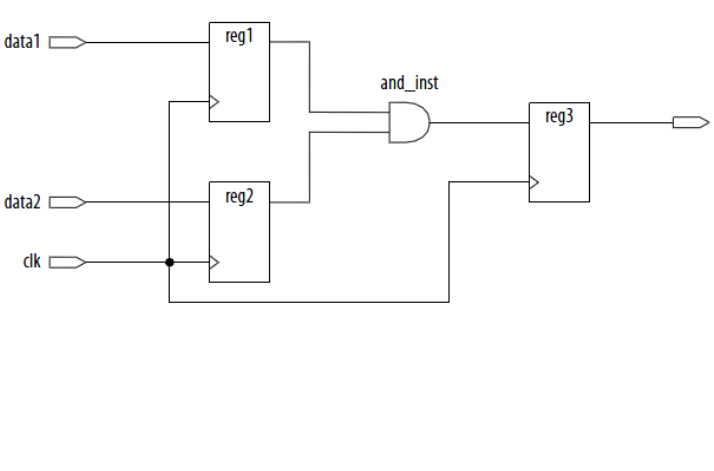

在FPGA 设计中,很少进行细致全面的时序约束和分析,Fmax是最常见也往往是一个设计唯一的约束。这一方面是由FPGA的特殊结构决定的,另一方面也是由于缺乏好用的工具造成的。好的时序约束可以指导布局布线工具进行权衡,获得最优的器件性能,使设计代码最大可能的反映设计者的设计意图。

花些功夫在静态时序分析上既可以保证设计质量,也可以促使设计者再认识自己的代码。这后一点,对于我们这些逻辑设计初学者来说,尤为重要。从门级(在Altera的FPGA器件中是LE 级)再认识自己的代码,可以更深入地体会语言的特点,也可以更深入地理解综合工具对语言的处理,对于设计能力的提高帮助很大。

1. 基本术语和概念

1.1 网表基本单元

· 节点(nodes)

包含了大部分基本的时序网表单元,常常代表端口、引脚和寄存器。

· 单元(cells)

Altera 器件中的基本结构单元(例如,查找表、寄存器、IO 单元、PLL、存储器块等),LE 可以看作是Cell。

· 引脚(pins)

基本结构单元cell的输入输出,这里不包括器件的物理引脚。

· 连线(nets)

两个pin之间的连线。(参考文献《timequest就一定要搞定

》中的定义与官方手册中好像略有不同,文献中定义是:同一个Cell中,从输入Pin到输出Pin经过的逻辑。特别注意:网表中连接两个相邻Cell的连线不被看作Net,被看作同一个点,等价于Cell的Pin。还要注意:虽然连接两个相邻Cell的连线不被看作Net,但是这个连线还是有其物理意义的,等价于Altera器件中一段布线逻辑,会引入一定的延迟(IC,Inter-Cell)。)

· 端口(ports)

顶层逻辑的输入输出端口。对应已经分配的器件引脚。

· 时钟(clock)

约束文件中指定的时钟,不仅指时钟输入引脚,还包括内部时钟。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章