资料下载

静态时序分析的基础与应用的详细说明

在制程进入深次微米世代之后,晶片(IC)设计的高复杂度及系统单晶片(SOC)设计方式兴起。此一趋势使得如何确保IC品质成为今日所有设计从业人员不得不面临之重大课题。静态时序分析(Static Timing Analysis简称STA)经由完整的分析方式判断IC是否能够在使用者的时序环境下正常工作,对确保IC品质之课题,提供一个不错的解决方案。然而,对于许多IC设计者而言,STA是个既熟悉却又陌生的名词。本文将力求以简单叙述及图例说明的方式,对STA的基础概念及其在IC设计流程中的应用做详尽的介绍。

什么是STA?

STA的简单定义如下:套用特定的时序模型(Timing Model),针对特定电路分析其是否违反设计者给定的时序限制(Timing Constraint)。以分析的方式区分,可分为Path-Based及Block-Based两种。

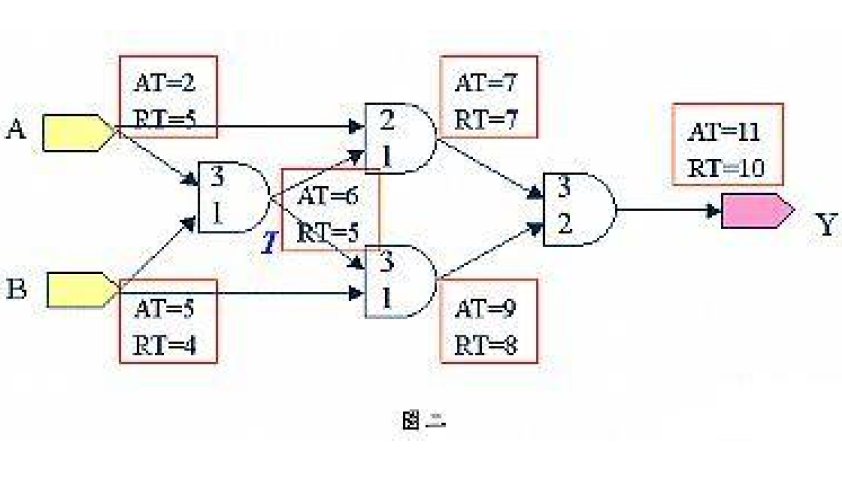

先来看看Path-Based这种分析方式。如图一所示,讯号从A点及B点输入,经由4个逻辑闸组成的电路到达输出Y 点。套用的Timing Model标示在各逻辑闸上,对于所有输入端到输出端都可以找到相对应的延迟时间。而使用者给定的Timing Constraint为:

1. 讯号A到达电路输入端的时间点为2(AT=2,AT为Arrival Time)。

2. 讯号B到达电路输入端的时间点为5(AT=5)。

3. 讯号必须在时间点10之前到达输出端Y(RT=10,RT为Required Time)。

现在我们针对P1及P2两条路径(Path)来做分析。P1的起始点为A,讯号到达时间点为2。经过第1个逻辑闸之后,由于此闸有2单位的延迟时间,所以讯号到达此闸输出的时间点为4(2+2)。依此类推,讯号经由P1到达输出Y的时间点为7(2+2+3)。在和上述第三项Timing Constraint比对之后,我们可以得知对P1这个路径而言,时序(Timing)是满足使用者要求的。

按照同样的方式可以得到讯号经由路径B到达输出Y的时间点为11(5+1+3+2),照样和上述第三项Timing Constraint比对,我们可以得知对P2这个路径而言,Timing是不满足使用者要求的。

对图一的设计而言,总共有6个讯号路径。对于采用Path-Based分析方式的STA软体来说,它会对这6个讯号路径作逐一的分析,然后记录下结果。IC设计者藉由检视其分析报告的方式来判断所设计的电路是否符合给定的Timing Constraint。由于最常用来做静态时序分析验证核可(STA Signoff)的EDA软

体PrimeTime?采用Path-Based的分析方式,所以本文将以Path-Based的分析方式介绍为主。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章