资料下载

手把手教你学FPGA语法篇

当前业界的硬件描述语言中主要有VHDL 和Verilog HDL。根据当前 ASIC/FPGA设计现有的特点、现状,Verilog HDL 语言已经成为决定的主导语言,使用Verilog HDL,可以统一ASIC/FPGA设计平台,简化流程,本人经历了几个大型芯片项目,包括所有的代码/IP都没有一句是VHDL,全部是Verilog HDL。使用VHDL的人非常非常少,只有部分学校在教学,如果您还在使用VHDL,那么当您看到本篇教程的时候,请马上切换过来。

当前的数字电路设计从层次上分可分成以下几个层次: 1. 算法级设计:利用高级语言如C语言及其他一些系统分析工具(如MATLAB)对设计从系统的算法级方式进行描述。算法级不需要包含时序信息。 2. RTL级设计:用数据流在寄存器间传输的模式来对设计进行描述。 3. 门级:用逻辑级的与、或、非门等门级之间的连接对设计进行描述。 4. 开关级:用晶体管和寄存器及他们之间的连线关系来对设计进行描述。算法级是高级的建模,一般对特大型设计或有较复杂的算法时使用,特别是通讯方面的一些系统,通过算法级的建模来保证设计的系统性能。在算法级通过后,再把算法级用RTL级进行描述。门级一般对小型设计可适合。开关级一般是在版图级进行。最常使用的是RTL级别的设计,90%以上的数字电路都是采用RTL级别进行设计。

硬件描述语言

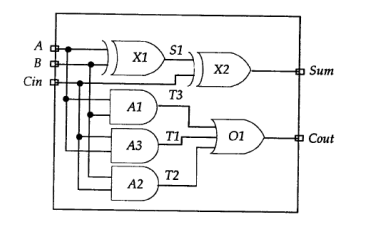

硬件描述语言HDL(Hardware Description Language )是一种用形式化方法来描述数字电路和数字逻辑系统的语言。数字逻辑电路设计者可利用这种语言来描述自己的设计思想,然后利用EDA工具进行仿真,再自动综合到门级电路,最后用ASIC或FPGA实现其功能。举个例子,在传统的设计方法中,对2输入的与门,我们可能需到标准器件库中调个74系列的器件出来,但在硬件描述语言中, “& ”就是一个与门的形式描述,“C = A & B”就是一个2输入与门的描述。而 “and”就是一个与门器件。硬件描述语言发展至今已有二十多年历史,当今业界的标准中(IEEE标准)主要有VHDL和Verilog HDL 这两种硬件描述语言。

Verilog HDL 语言最初是于1983 年由Gateway Design Automation 公司为其模拟器产品开发的硬件建模语言。那时它只是一种专用语言。由于他们的模拟、仿真器产品的广泛使用,Verilog HDL作为一种便于使用且实用的语言逐渐为众多设计者所接受。在一次努力增加语言普及性的活动中,Verilog HDL 语言于 1990 年被推向公众领域。Open Verilog International(O V I )是促进Verilog 发展的国际性组织。1992 年,OVI 决定致力于推广Verilog OVI 标准成为IEEE 标准。这一努力最后获得成功,Verilog 语言于1995 年成为IEEE 标准,称为IEEE Std1364-1995 。完整的标准在Verilog 硬件描述语言参考手册中有详细描述。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章