资料下载

×

使用FPGA实现DVI输出图像选区截取的详细资料说明

消耗积分:0 |

格式:rar |

大小:0.34 MB |

2021-01-22

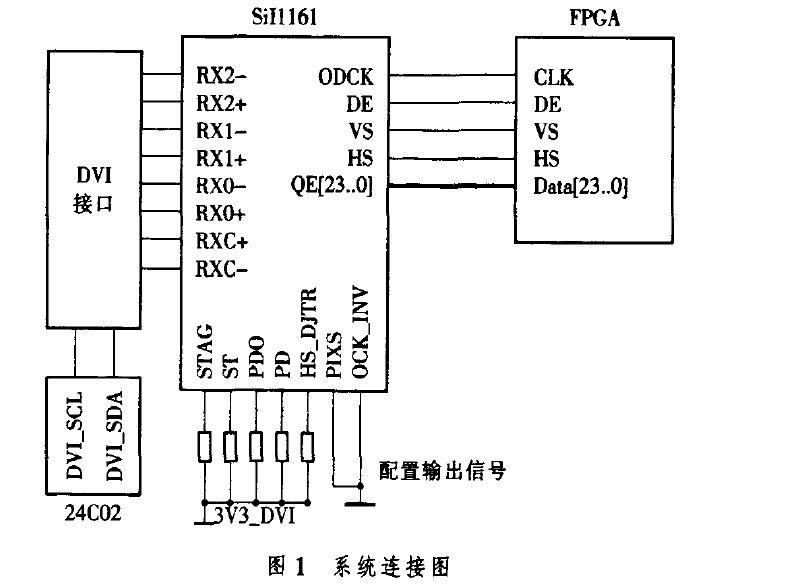

介绍了数字视频接口(DVI)解码芯片Silll61的功能及其外围配置、DDC通道及编辑EDID的方法,阐述了在FPGA中依据VESA Monitor Timing标准,利用有限状态机进行数据截取的过程,经验证DVI输出的选区图像达到了在LED大屏幕上实时显示的效果。

LED全彩显示屏是LED产业的高端产品,为提高产品的市场竞争力,必须提高视频显示效果、改善色彩还原性,对其显示控制单元的设计提出了很高的要求。LED全彩显示屏的显示控制单元须实现数字视频解码、数据处理与传输、显示驱动等功能。

DVI在LED大屏幕显示系统中得到了广泛应用,DVI接口输出的图像是PC机显示器的全屏数据,分辨力为l 024x768或800x600等,而一般场所中使用的LED全彩显示屏其分辨力往往达不到1 024×768,因此需要对DVI接口输出的帧图像进行选区截取,保留选定区域的有效像素数据。

为解决该问题,在理解DVI规范、掌握DVI解码芯片Silll61用法的基础上,采用FPGA实现了DVI接口输出视频图像的选区截取功能,经实验验证效果良好。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章