资料下载

×

如何实现两块FPGA之间的通信总结

消耗积分:0 |

格式:rar |

大小:0.64 MB |

2021-02-25

1、两块fpga 之间采用12 根线连接,包括8 根数据线, 2 根同步时钟线, 2 根使能信号线。

2、每块fpga 的引脚配置为[3:0]rxd (接受数据) , rxc(接受时钟) , rxen(接受使能信号) ,[3:0]txd , txc, txen。

3、采用全双工通信。

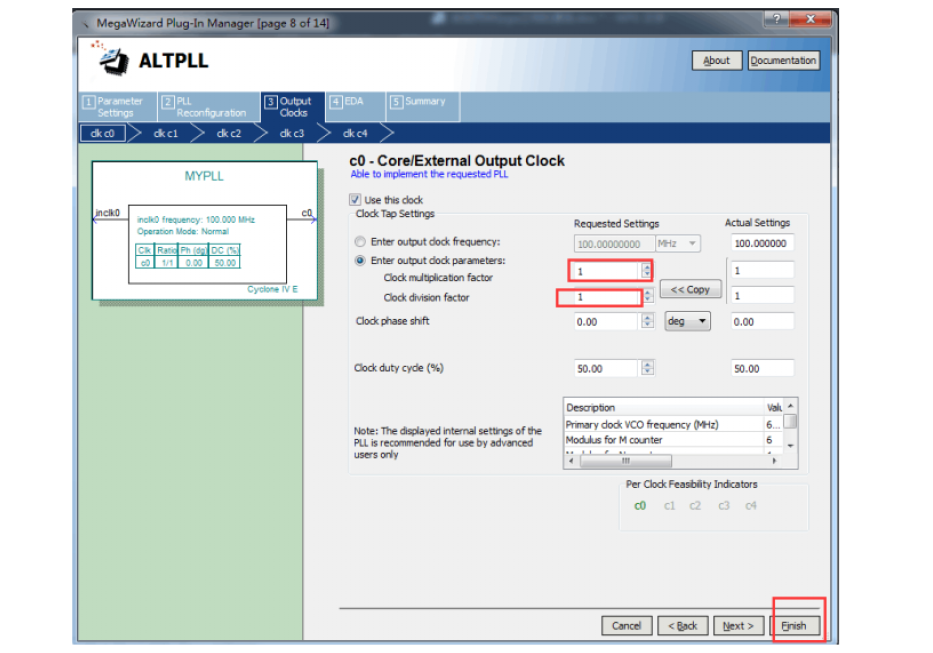

4、同步时钟均采用锁相环产生时钟,在末尾有产生过程。

5、相互之间发送的数据为0~255,不过本程序没加上使能信号。

6、下面附上我的程序。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章