资料下载

什么是低压降稳压器(LDO)的压降? - 第五部分

之前在文章中,我们探讨了“现实中的电源抑制比(PSRR) - 第四部分”,通过示例讲解PSRR参数。

往期文章

什么是 LDO 噪声?第一部分

什么是积分噪声?-第二部分

什么是 PSRR?- 第三部分

现实中的电源抑制比(PSRR) - 第四部分

本文章继续此系列,将聚焦“低压降”的含义,并介绍低压降和极低压降值的LDO产品和方案。您的应用需要低压降的LDO吗?我们将讲解压降的含义,如何测量以及具有标准压降和极低压降的LDO之间的差异。

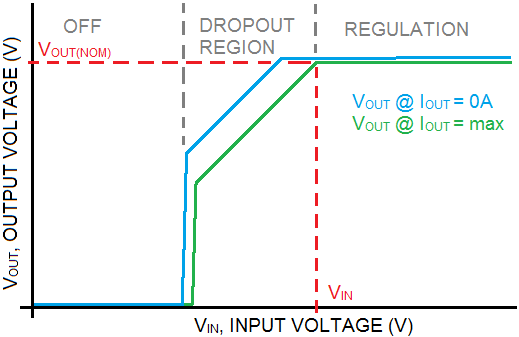

LDO必须具有比压降参数更高的裕量VIN – VOUT。压降是LDO正常运行的最关键参数之一。压降是LDO需要适当调节的VDO = VIN – VOUT,NOM的差。VOUT,NOM是LDO处于稳压状态时在输出端的输出电压标称值。

压降值通常在VOUT低于标称值(约3%)或100 mV时测量。当VOUT下降时,如约100mV,很容易测量该值。通常针对标称输出电流测量压降参数,因为压降是在VOUT下降(比VOUT,NOM低约3%)时测量的。

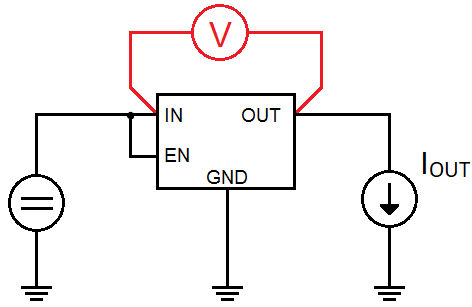

因此,必须在灌电流模式下将输出连接到电流源,例如,将有源负载连到恒定灌电流。如果电阻连接到输出,则负载输出电流将减小,并且测量无效,请参见下图。

LDO应该在VIN和VOUT有一个电压差,并具有较高的VDO 压降值,以实现好的动态性能。

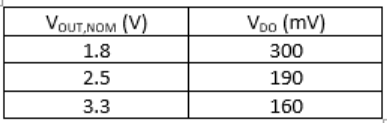

大多数LDO有导通器件P沟道MOSFET(PMOS),这对于较低的输出电压来说有点不利。当标称输出电压VOUT,NOM较低时,带PMOS导通器件的LDO的压降VDO会增加。

举例来说,请看下表,假设我们正在使用NCP161。您可以看到1.8 V选项的压降值远高于3.3 V选项。

PMOS器件LDO有缺点,因为它们具有相当高的最小输入电压VIN,MIN110也是PMOS器件LDO,VIN低。VIN,MIN = 1.1V。NCP110的最低输出电压选项0.6 V的压降值为500 mV。

如果要求非常低的压降或接近0 V的输出电压选项,则可以使用偏置轨LDO。这种LDO有导通器件N沟道MOSFET(NMOS),它需要连接比VOUT高约1 V – 2 V的辅助电源VBIAS,以实现极低的压降。

偏置轨LDO与普通LDO的结构相同,但内部模块(除导通器件的所有器件)的电源未连接至VIN。它单独作为次级电源。

这些器件的一些示例是NCP130、NCP134、NCP137和NCP139。与带PMOS导通器件的LDO相比,带NMOS导通器件的LDO具有几乎不受输出电压影响的压降。

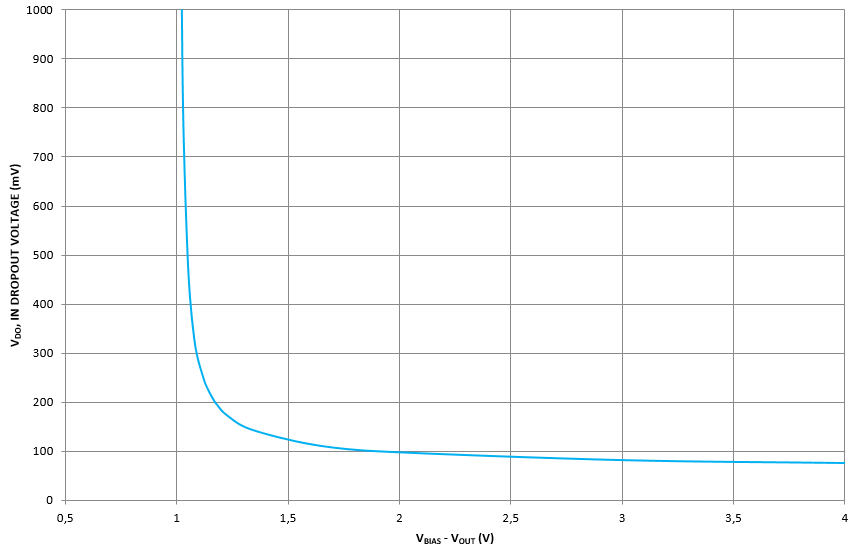

这些器件在额定输出电流下的VDO压降值在40 mV〜150 mV范围内。但是必须如上所述连接VBIAS电压,否则由于伏特单位,压降会高得多。

在下图中,您可以看到当VBIAS - VOUT差减小时,NCP134的压降会怎样,这样,VBIAS电压不够高。

BIAS - VOUT)">

BIAS - VOUT)">也可以使LDO带导通器件NMOS但不提供VBIAS电源。有一个电荷泵用于为内部模块供电。电荷泵器件从VIN电源产生高两倍的内部VBIAS电压。

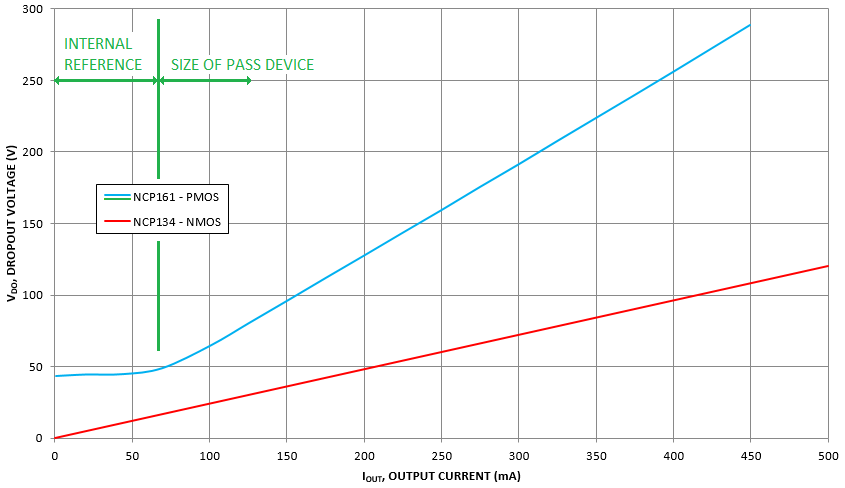

在图4中,您可看到带PMOS导通器件的LDO和带NMOS导通器件的LDO的压降差。带PMOS导通器件的LDO通常在零输出电流时具有非零压降值。LDO压降的这一部分是内部参考电压的压降。

第二部分是通过导通器件的尺寸设置的压降。带NMOS导通器件的LDO具有由VBIAS电压提供的内部基准。因此,它没有第一部分。带NMOS导通器件的LDO压降仅通过导通器件的尺寸设置。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章