资料下载

硬件即代码第三部分:空间与时间

描述

在本周的部分中,一切都与性能有关。FPGA 的常见用途之一是提高速度和/或能源效率方面的性能。这部分是通过 1) 消除指令的解释开销,2) 消除中央内存瓶颈,以及 3) 指令级并行性来实现的。

如果您是本系列的新手,您可能想返回到Hardware-as-Code Part I 。

示例 1 的性能

在第二部分中,我们生成了以下简单功能的硬件实现:

int16_t calc(int16_t x) {

return 7 * x - 15;

}

让我们仔细看看这个函数作为在 CPU 上执行的软件和作为 FPGA 上的自定义硬件函数的性能。首先,考虑用于在 CPU 上执行此功能的能量。典型的小型 CPU 将由以下功能硬件块组成:

- 1.取指令

- 2.指令解码

- 3. 内存参数获取

- 4.执行指令

- 5. 写回结果

其中前两个被 FPGA 功能完全消除。这些纯粹是 CPU 模型所需的解释开销。3 号和 4 号专用于中央存储器模型所需的数据移动。FPGA 通常不需要外部存储器,这将再次完全消除开销。4 号是 CPU 中唯一实际执行特定应用功能的部分。然而,所有这些单元在整个程序执行过程中都在不断地消耗能量。此外,外部存储器也消耗大量电力。

执行时间呢?让我们估计一下在小型 CPU 上执行可能需要的周期数:

- 将 x 加载到寄存器中(2 个周期)

- 将第一个常数加载到寄存器中(1 个周期)

- 乘法(1 个周期)

- 将第二个常数加载到寄存器中(1 个周期)

- 添加(1个周期)

- 将结果存储到内存(2 个周期)

总共8个周期!当然,对于具有更大指令集和更复杂指令的 CPU,您可能可以使用更少的指令,但这些通常需要更多的周期。因此,假设 4-8 个周期。

现在对于 FPGA 实现,我们有一个执行乘法和加法的单周期电路。这就像有一个专门为这个应用程序构建的自定义指令。值通过寄存器传递,没有内存访问。CPU 有时可以利用寄存器来传递值,但通常只有少数可用。此外,许多函数需要堆栈内存来存储局部变量和临时值。

不服气?让我们稍微扩展第一个例子来解决一个现实世界的问题,看看它是如何比较的。

机器学习分类示例

分类是机器学习执行的一项非常常见的任务。分类任务是根据您拥有的一些数据将某事物分类为 2 个或更多类。例如,根据附在风扇上的一些振动传感器数据,将其分类为工作或不工作(电机故障/螺旋桨卡住)。

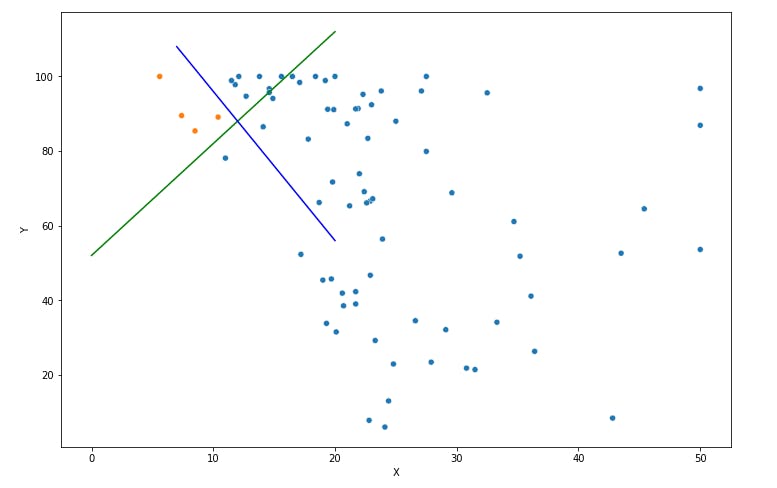

让我们根据两个测量值将一些数据简单地分类为两个类别。下图显示了许多具有已知类别的对象的测量数据。

每个点代表一个示例对象的两个测量值,颜色代表该对象的已知类别。目标是,根据一个新对象的两个值(x,y),预测它是在橙色类还是蓝色类中。从图中可以看出,橙色的类对象都在绿线和蓝线的左侧。蓝色类对象都在一条或两条线的右侧。

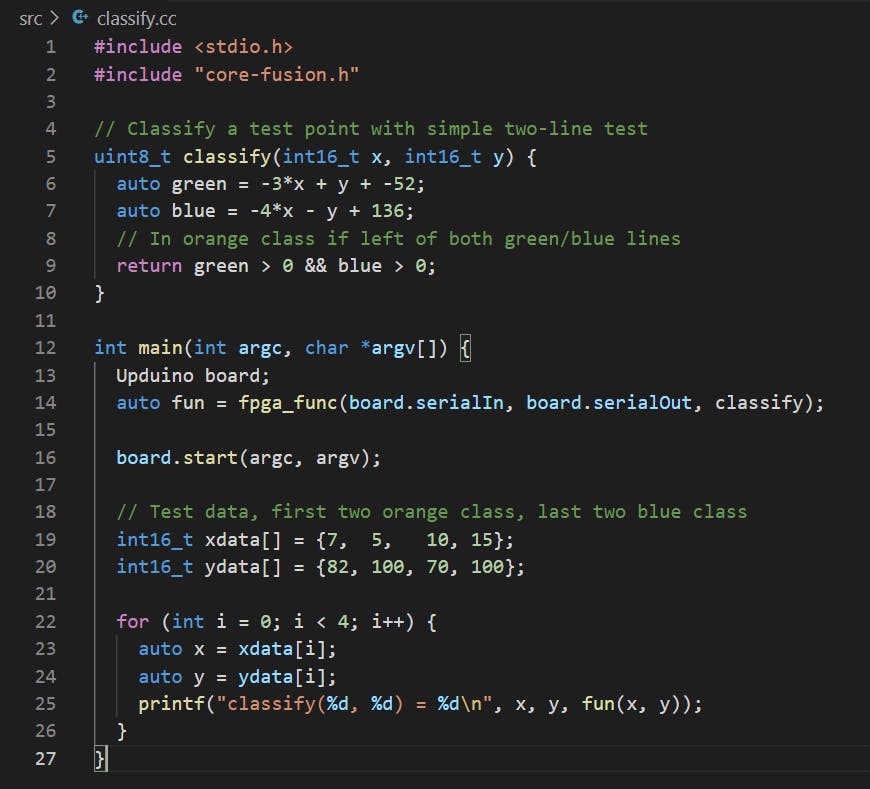

让我们实现一个简单的预测函数,它只测试一个新点是否在两条线的左侧:

此代码也可从 git repo 获得:文件夹中的https://github.com/sathibault/hac-examples.git 。poly-classify

继续classify 在您的计算机和 FPGA 板上构建和测试此功能(如果您需要查看它是如何完成的,请返回第 II 部分)。您应该看到如下输出:

poly-classify>.\program

classify(7, 82) = 1

classify(5, 100) = 1

classify(10, 70) = 0

classify(15, 100) = 0

输出 1 表示该点位于两条线的左侧,预测的类为橙色。否则,预测类别为蓝色。

我选择这个例子是因为它很容易解释,并且非常代表当今使用的非常成功的神经网络所需的计算。

指令级并行

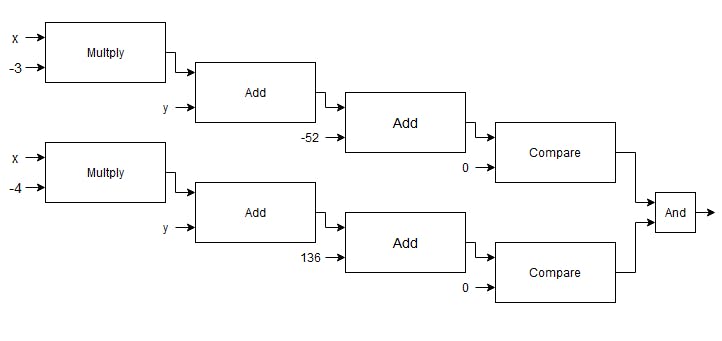

除了消除中央内存瓶颈和 CPU 的解释开销外,定制硬件还支持高级别的指令级并行性。对于第二个示例,为classify函数生成的硬件如下所示:

如您所见,每个方程都有自己专用的乘法器和加法器。尽管相对于第一个示例,我们所做的工作量增加了四倍,但整个函数仍然在一个周期内执行!通常对应于 CPU 上的许多指令并按顺序执行的功能可以并行执行。试着估计一下我的指令/周期这个函数在 CPU 上需要多少。

我真的在强调 CPU 方法的负面影响,但对于 FPGA 来说,这并不全是玫瑰。我们可以在速度和功耗方面取得一些显着的进步,但缺点是它占用了物理空间。上图中的每个模块都占用了 FPGA 上的空间。随着函数的增长,它将占用的空间量也会增加,并且可用的空间有限。虽然空间也可能是微控制器程序存储器的一个问题,但 FPGA 的空间限制通常更加有限。我们将在下一期中更详细地研究空间使用情况。

下一步

到目前为止,我们一直在研究简单的直线代码示例。下一次,我们将看看循环和数组的使用。

连接

在我发布新的分期付款时,请关注我以保持最新状态。还有一个 Discord 服务器(公共聊天平台),用于您在https://discord.gg/3sA7FHayGH上可能有的任何评论、问题或讨论

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章