资料下载

×

基于FPGA的DDS IP核设计方案

消耗积分:0 |

格式:pdf |

大小:809 KB |

2012-04-05

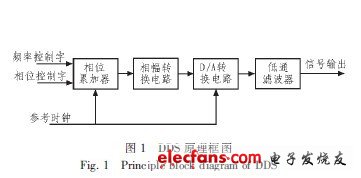

以Altera公司的Quartus Ⅱ 7.2作为开发工具,研究了基于FPGA的DDS IP核设计,并给出基于Signal Tap II嵌入式逻辑分析仪的仿真测试结果。将设计的DDS IP核封装成为SOPC Builder自定义的组件,结合32位嵌入式CPU软核Nios II,构成可编程片上系统(SOPC),利用极少的硬件资源实现了可重构信号源。该系统基本功能都在FPGA芯片内完成,利用 SOPC技术,在一片 FPGA 芯片上实现了整个信号源的硬件开发平台,达到既简化电路设计、又提高系统稳定性和可靠性的目的。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章