资料下载

×

最大限度地减少抖动/相位时钟分布拓扑噪声对无线性能的关键

消耗积分:0 |

格式:rar |

大小:0.08 MB |

2017-05-12

最大限度地减少抖动/相位时钟分布拓扑噪声对无线性能的关键

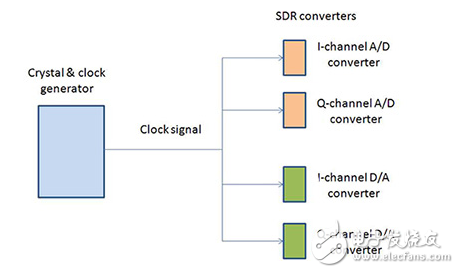

RF电路的所有模拟设计的日子已经过去了,今天的RF设计依赖于沉重的数字功能,如基于PLL的合成器(调谐器)和A / D和D / A转换器。越来越多,这些合成器和转换器被直接使用在更高的频率,更宽的带宽,并为直接转换设计或软件定义无线电(SDR)。

其结果是,时钟,它所看到的ICS支持,必须更加“纯粹”比以往任何时候都。为什么会这样?其原因是,时钟中的任何偏差,通常其特征在于定时抖动或相位噪声,将降低可实现的组件性能。时钟抖动和相位噪声,有效位数(ENOB)一个A / D转换器将低于其标称的分辨率,和其他参数如动态范围,信噪比,失真和互调产物也将受到不利影响。允许的数字是惊人的紧:在许多最新的设计,允许的最大时钟抖动在负载电路是几个FSEC秩序。

[Note that timing jitter and phase noise are two equally legitimate perspectives on the same imperfection, with jitter being a time-domain number while phase noise is a frequency-domain number. Depending on the error analysis, designers need to use one or the other, but neither factor is inherently a superior way of looking at clock issues.]

For these reasons, designs place a great deal of emphasis on producing and delivering a high-accuracy clock for the various ICs which require them. It is not just a matter of generating the clock, as a quality crystal in conjunction with various high-end clock-oscillator/generator ICs can provide the clock needed. The real challenge is ensuring the clock signals reach the loads intact, without noise or jitter.

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章