资料下载

×

系数存取机制技术

消耗积分:0 |

格式:rar |

大小:0.14 MB |

2017-05-25

音频转换器的新家庭功能增强过滤功能,其中包括使用双缓冲系数机制所需的写入系数。这一机制在这个应用报告中讨论了系数存储器访问的其他方面。

DAC系统的访问

DAC通道系数存储空间(C-RAM)由两个缓冲器:缓冲器和Buffer B.控制接口访问这些缓冲取决于操作模式(即非适应性或自适应)以及PRB或minidsp_d电源状态。

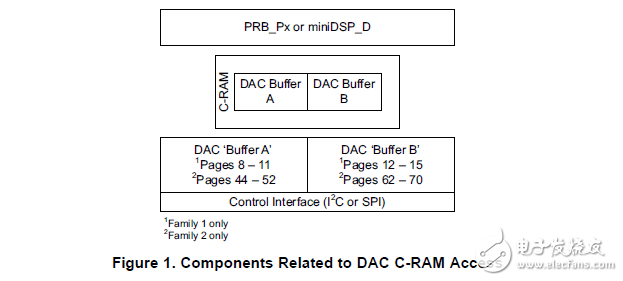

图1显示了与系数存储器访问有关的三个组件:

•PRB或minidsp_d–他们访问系数存储器执行信号处理。系统访问取决于操作模式。

•C-RAM–存储系数数据是由PRB访问(或minidsp_d)或控制接口。

•控制界面-控制界面有两个多功能银行的页面,提供访问该系统缓冲区。这些银行被表示为缓冲A和Buffer B,虽然他们不在某些操作模式中,必须访问标记的缓冲区。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章