资料下载

飞思卡尔半导体技术数据MPC5200B数据表

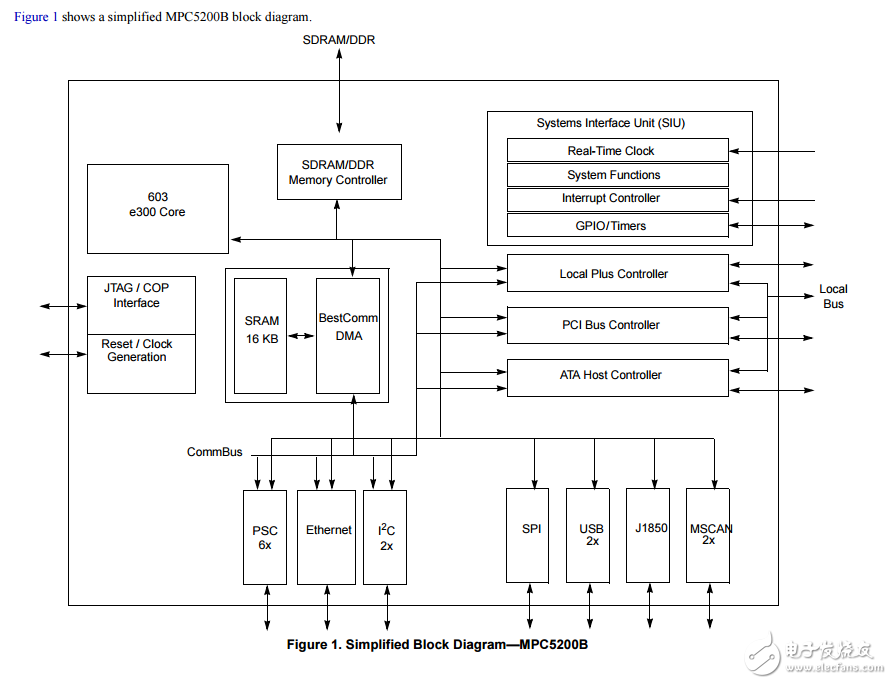

Key features are shown below. • MPC603e series e300 core – Superscalar architecture – 760 MIPS at 400 MHz (–40 o C to +85 o C) – 16 KB Instruction cache, 16 KB Data cache – Double precision FPU – Instruction and Data MMU – Standard and Critical interrupt capability • SDRAM / DDR Memory Interface – Up to 133 MHz operation – SDRAM and DDR SDRAM support – 256 MB addressing range per CS, two CS available – 32-bit data bus – Built-in initialization and refresh • Flexible multi-function External Bus Interface – Supports interfacing to ROM/Flash/SRAM memories or other memory mapped devices – 8 programmable Chip Selects – Non-multiplexed data access using 8-/16-/32-bit databus with up to 26-bit address – Short or Long Burst capable – Multiplexed data access using 8-/16-/32-bit databus with up to 25-bit address • Peripheral Component Interconnect (PCI) Controller – Version 2.2 PCI compatibility – PCI initiator and target operation – 32-bit PCI Address/Data bus – 33 and 66 MHz operation – PCI arbitration function • ATA Controller – Version 4 ATA compatible external interface—IDE Disk Drive connectivity • BestComm DMA subsystem – Intelligent virtual DMA Controller – Dedicated DMA channels to control peripheral reception and transmission – Local memory (SRAM 16 KB) • 6 Programmable Serial Controllers (PSC) – UART or RS232 interface – CODEC interface for Soft Modem, Master/Slave CODEC Mode, I2S and AC97

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章