资料下载

10MHz带宽640MSPS双连续时间调制器AD9267数据表

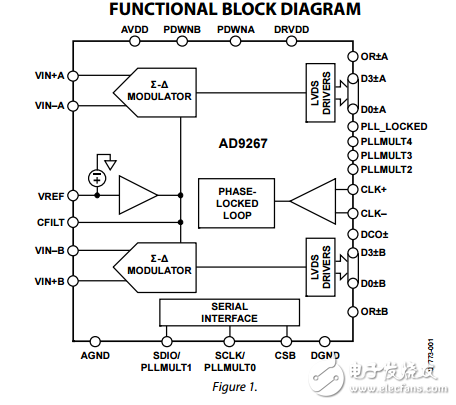

The AD9267 is a dual continuous time (CT) sigma-delta (Σ-Δ) modulator with −88 dBc of dynamic range over 10 MHz real or 20 MHz complex bandwidth. The combination of high dynamic range, wide bandwidth, and characteristics unique to the continuous time Σ-Δ modulator architecture makes the AD9267 an ideal solution for wireless communication systems. The AD9267 has a resistive input impedance that significantly relaxes the requirements of the driver amplifier. In addition, a 32× oversampled fifth-order continuous time loop filter attenuates out-of-band signals and aliases, reducing the need for external filters at the input. The low noise figure of 15 dB relaxes the linearity requirements of the front-end signal chain components, and the high dynamic range reduces the need for an automatic gain control (AGC) loop. A differential input clock controls all internal conversion cycles. An external clock input or the integrated integer-N PLL provides the 640 MHz internal clock needed for the oversampled continuous time Σ-Δ modulator. The digital output data is presented as 4-bit, LVDS at 640 MSPS in twos complement format. A data clock output (DCO) is provided to ensure proper latch timing with receiving logic. Additional digital signal processing may be required on the 4-bit modulator output to remove the out-of-band noise and to reduce the sample rate.

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章