资料下载

×

基于FPGA的数字存储示波器设计与实现

消耗积分:0 |

格式:rar |

大小:0.3 MB |

2017-10-18

数字存储示波器作为测试技术的重要,工具,被广泛应用于各个领域,并逐步取代传统模拟示波器。其采样数据是波形运算和分析的基础,直接影响到整个数字存储示波器的准确性。从这点出来,提出采用现场可编程逻轧器件(FPGA)作为数字存储示波器采样控制系统的核心,从芯片间有效协助的角度,基于FPGA 设计ARM 接[ ]通信控制模块和外围芯片驱动功能模块,以FPGA 为核心有效地组织其它芯片,共同完成数字存储示波器数据采样过程,确保数据按需求采样,有效地提高数字存储示波器的采样效率和数据的可靠性。

1数字存储示波器的总体设计方案

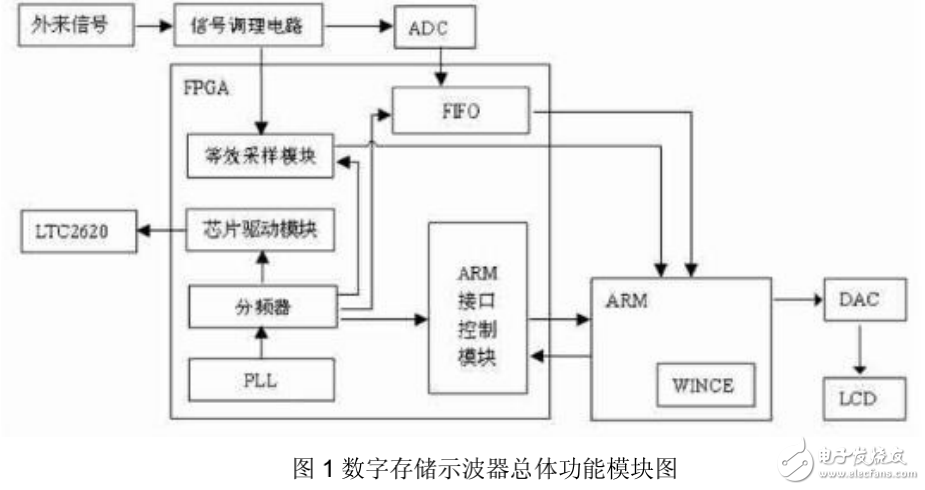

数字存储示波采用双处理器(ARM+FPGA)的嵌入式系统设计方案,ARM 内嵌WINCE操作系统,整个采样系统主要在FPGA 里完成,从功能的角度分成采样信息处理子系统与采样控制子系统,本文着重介绍采样控制子系统的驱动部分,由ARM 接[ ]控制模块与芯片驱动模块组成。如图1所示:

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章