资料下载

×

实例分析并行信号处理系统的设计方案

消耗积分:1 |

格式:rar |

大小:0.4 MB |

2017-10-20

自数字计算机问世以来,计算机的处理能力已经增长了100 k倍以上。然而,现有性能最高的计算机的计算能力仍远远不能满足人类对计算速度无止境的追求。

在科学计算、地质分析、气象预测、仿真模拟、图像处理以及实时信号处理领域,对计算机处理速度的要求尤为迫切。随着半导体技术的迅速发展,采用超大规模集成电路设计的处理单元功能越来越强,然而单处理器性能的提高受到了诸多限制。因此,满足对运算速度的巨大需求目前只能通过并行处理技术来实现。

1 概述

本文中设计了一种并行信号处理系统,其主要特点是:

(1)具有强大的处理能力,可以完成多种信号处理模式。

(2)信号处理功能通过大量信号处理芯片(DSP)的并行计算完成。

(3)信号处理功能的改变通过软件实现。

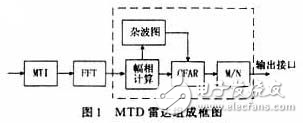

图1所示的是动目标检测雷达信号处理机的主要组成部分,虚线中的处理模块是本文要完成的工作。

2 幅相计算、CFAR检测、M/N检测

2.1 幅相计算

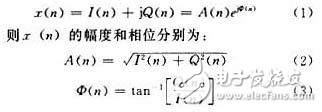

幅相计算指从复数据计算其幅度和相位,假使:

2.2 CFAR检测和M/N检测

雷达信号的检测总是在干扰背景上进行的,为了在强干扰中提取信号,不仅要求有一定的信噪比,而且必须有恒虚警处理设备,恒虚警处理的目的是保持信号检测时的虚警率恒定,这样才能使处理机不致因虚警太多而过载。

(1)单元平均恒虚警(CFAR)检测器

已经知道,在低分辨率的脉冲雷达中,海浪和雨雪等分布杂波可以看作很多独立照射单元回波的迭加,因而杂波包络的分布服从瑞利分布,如果检测背景中存在此类杂波,检测门限可以通过计算杂波的均值得到,但是由于杂波在空间分布的未知性,求杂波均值只能从被检测目标邻近单元来获得,这就是比较常用的单元平均CFAR检测器。为了减少这类检测器在杂波边缘内侧虚警显著增大问题,一般采用其改进电路—两侧单元平均选大电路,如图2所示。在被检测单元的两边,为了防止目标本身对门限值的影响各空出了一个保护单元。

在科学计算、地质分析、气象预测、仿真模拟、图像处理以及实时信号处理领域,对计算机处理速度的要求尤为迫切。随着半导体技术的迅速发展,采用超大规模集成电路设计的处理单元功能越来越强,然而单处理器性能的提高受到了诸多限制。因此,满足对运算速度的巨大需求目前只能通过并行处理技术来实现。

1 概述

本文中设计了一种并行信号处理系统,其主要特点是:

(1)具有强大的处理能力,可以完成多种信号处理模式。

(2)信号处理功能通过大量信号处理芯片(DSP)的并行计算完成。

(3)信号处理功能的改变通过软件实现。

图1所示的是动目标检测雷达信号处理机的主要组成部分,虚线中的处理模块是本文要完成的工作。

2 幅相计算、CFAR检测、M/N检测

2.1 幅相计算

幅相计算指从复数据计算其幅度和相位,假使:

2.2 CFAR检测和M/N检测

雷达信号的检测总是在干扰背景上进行的,为了在强干扰中提取信号,不仅要求有一定的信噪比,而且必须有恒虚警处理设备,恒虚警处理的目的是保持信号检测时的虚警率恒定,这样才能使处理机不致因虚警太多而过载。

(1)单元平均恒虚警(CFAR)检测器

已经知道,在低分辨率的脉冲雷达中,海浪和雨雪等分布杂波可以看作很多独立照射单元回波的迭加,因而杂波包络的分布服从瑞利分布,如果检测背景中存在此类杂波,检测门限可以通过计算杂波的均值得到,但是由于杂波在空间分布的未知性,求杂波均值只能从被检测目标邻近单元来获得,这就是比较常用的单元平均CFAR检测器。为了减少这类检测器在杂波边缘内侧虚警显著增大问题,一般采用其改进电路—两侧单元平均选大电路,如图2所示。在被检测单元的两边,为了防止目标本身对门限值的影响各空出了一个保护单元。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章