资料下载

×

基于FPGA和DSP组合的无线基站分析

消耗积分:1 |

格式:rar |

大小:0.6 MB |

2017-10-25

FPGA和DSP之间的“智能配分”可使无线系统设计师获得最佳性能组合和成本——效能。应用DSP和FPGA组合可使成本降低。对于无线基站,组合有DSP可编程逻辑的系统配分,可促使更大的产品设计和市场成功率。

更高数据率的需求正在驱使无线蜂窝系统从窄带2G GSM,IS-95系统到W-CDMA基3G和3.5G系统(支持高达10Mbps峰值数据率)变革。将来,3Gpp远期变革规范面向复杂的信号处理技术,如多输入多输出(MIMO)以及新的无线电技术(如正交频分多址OFDMA,多载波码分多址MC-CDMA)。这些技术对于实现超过吞吐量100Mbps的目标起关键作用。

另外的OFDM基宽带无线系统,如WiMAX现在传输速度超过70Mbps。靠较高级的调制技术和变速率信道编码可以实现数据率的改善。复杂的空间信号处理方法(包括聚束和MIMO无线技术)也是增加数据率的办法。然而,这种技术对基站设计师所产生的问题是:需要可缩放性、成本、效率和跨越多个标准的灵活性。

多可变目标

无线系统设计师需要满足大量关键技术要求,包括处理速度、灵活性、产品上市时间。所有这些要求决定对硬件平台的选择。主要的变量包括处理带宽、灵活性和降低成本的路径。

处理带宽

WiMAX与W-CDMA和CDM2000蜂窝系统相比,明显地具有较高的吞吐量和数据要求。为了支持这些较高的数据率,基础硬件平台必须具有宽处理带宽。另外,几种先进的信号处理技术,如快速傅里叶变换/快速傅里叶逆变换(FFT/IFFT)、聚束、MIMO、波峰因数缩减(CFR)、数字预失真(DPD)都是计算密集的,需要每秒几百万乘和累加运算。

灵活性

WiMAX是一个相当新的市场,现正处于开发和采用阶段。现在仍然不清楚在这很多移动宽带技术(WiMAX,Wibrow,Super3G,LTE,Ultra3G等)中,哪一种将被大量采用。

现在,末端产品灵活性和可编程性对多协议基站是关键性的。

降低成本的路径

对于OEM和服务供应商来讲,为了保持竞争力,最终产品的成本比灵活性更重要。在样机设计阶段选择正确的硬件平台,为生产制造提供无缝降低成本的路径,这会节省上百万工程成本。否则,需要重新设计系统。

系统结构的逻辑任务分配

控制、信号处理和数据通路运行构成无线基站中处理负载的主体。实现这些功能的最通用方法是采用微控制器(MCU)、FPGA和可编程DSP的组合。MCU控制系统、而FPGA和DSP控制数据流处理。DSP软件实现系统的轻载处理要求和定向控制任务。重载最好的实现方法是用FPGA,因为FPGA具有很强的并行处理能力。

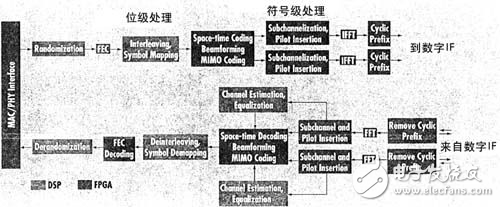

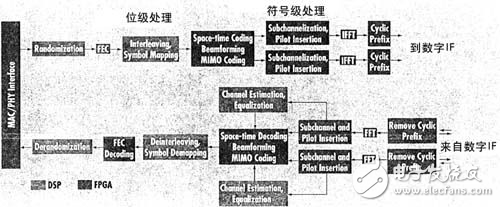

组合的DSP和FPGA确保整个系统的灵活性,并提供重新可编程性以确定系统缺陷,而且支持不同的标准。DSP和FPGA之间的分配策略依赖于处理要求、系统带宽、系统配置、发射和接收天线数。图1示出OFDMA基系统(如WiMAX或LTE)中基带物理层(PHY)功能的典型DSP/FPGA分配。

图1 OFDMA系统中DSP/FPGA分配

包含先进的多天线技术,这类系统所提供的吞吐量可达到75~100MPS。基带PHY功能可大致分为位级(bit-level)处理和符号级(Symbol-level)处理功能。

位级处理

位级处理单元包括发射端的随机化、前向纠错(FEC)、到四相相移键控(QPSK)和正交调幅(QAM)功能的交织和变换。相应的接收处理位级单元包括符号解变换、解交织、FEC解码和解随机性。

除FEC译码外的所有位级功能都是相当简单的,而且计算不是密集的。例如,随机性包含数据位的模2加法(借助简单伪随机二进制时序产生器输出)。尽管FPGA比固定总线宽度的DSP能为位级处理提供更大的灵活性。但是,低计算复杂性允许DSP处理这些功能。相比,FEC译码包括Viterbi译码、Turbo卷积译码、Turbo乘积译码和LDPC译码是计算密集的,而且DSP处理时会消耗有效带宽。

FPGA广泛用于卸载这些功能。同样FPGA也可用到MAC层的接口,以实现一定的较低MAC功能(如加密/解密和鉴别)。

符号级处理

OFDMA中的符号级功能包括子信道化和解子信道化、信道判断、均衡和循环前缀插入以及消除功能。时间—频率变换和频率—时间变换,分别用于FFT和IFFT实现。

信道判断和均衡可以离线执行,这涉及更多有关控制算法,适合用DSP实现。相反,FFT和IFFT功能是规则的数据通路功能,这包括非常高速下的复杂乘法,适合于用FPGA实现。

图2示出包含在高端FPGA(Altera公司StratixⅡ器件)内的嵌入式DSP单元。DSP处理器通常有多达8个专用乘法器,而StratixⅡ器件有多达384专用乘法器,提供的吞吐量高达346GMAC,这比现有的DSP高出一个量级。

更高数据率的需求正在驱使无线蜂窝系统从窄带2G GSM,IS-95系统到W-CDMA基3G和3.5G系统(支持高达10Mbps峰值数据率)变革。将来,3Gpp远期变革规范面向复杂的信号处理技术,如多输入多输出(MIMO)以及新的无线电技术(如正交频分多址OFDMA,多载波码分多址MC-CDMA)。这些技术对于实现超过吞吐量100Mbps的目标起关键作用。

另外的OFDM基宽带无线系统,如WiMAX现在传输速度超过70Mbps。靠较高级的调制技术和变速率信道编码可以实现数据率的改善。复杂的空间信号处理方法(包括聚束和MIMO无线技术)也是增加数据率的办法。然而,这种技术对基站设计师所产生的问题是:需要可缩放性、成本、效率和跨越多个标准的灵活性。

多可变目标

无线系统设计师需要满足大量关键技术要求,包括处理速度、灵活性、产品上市时间。所有这些要求决定对硬件平台的选择。主要的变量包括处理带宽、灵活性和降低成本的路径。

处理带宽

WiMAX与W-CDMA和CDM2000蜂窝系统相比,明显地具有较高的吞吐量和数据要求。为了支持这些较高的数据率,基础硬件平台必须具有宽处理带宽。另外,几种先进的信号处理技术,如快速傅里叶变换/快速傅里叶逆变换(FFT/IFFT)、聚束、MIMO、波峰因数缩减(CFR)、数字预失真(DPD)都是计算密集的,需要每秒几百万乘和累加运算。

灵活性

WiMAX是一个相当新的市场,现正处于开发和采用阶段。现在仍然不清楚在这很多移动宽带技术(WiMAX,Wibrow,Super3G,LTE,Ultra3G等)中,哪一种将被大量采用。

现在,末端产品灵活性和可编程性对多协议基站是关键性的。

降低成本的路径

对于OEM和服务供应商来讲,为了保持竞争力,最终产品的成本比灵活性更重要。在样机设计阶段选择正确的硬件平台,为生产制造提供无缝降低成本的路径,这会节省上百万工程成本。否则,需要重新设计系统。

系统结构的逻辑任务分配

控制、信号处理和数据通路运行构成无线基站中处理负载的主体。实现这些功能的最通用方法是采用微控制器(MCU)、FPGA和可编程DSP的组合。MCU控制系统、而FPGA和DSP控制数据流处理。DSP软件实现系统的轻载处理要求和定向控制任务。重载最好的实现方法是用FPGA,因为FPGA具有很强的并行处理能力。

组合的DSP和FPGA确保整个系统的灵活性,并提供重新可编程性以确定系统缺陷,而且支持不同的标准。DSP和FPGA之间的分配策略依赖于处理要求、系统带宽、系统配置、发射和接收天线数。图1示出OFDMA基系统(如WiMAX或LTE)中基带物理层(PHY)功能的典型DSP/FPGA分配。

图1 OFDMA系统中DSP/FPGA分配

包含先进的多天线技术,这类系统所提供的吞吐量可达到75~100MPS。基带PHY功能可大致分为位级(bit-level)处理和符号级(Symbol-level)处理功能。

位级处理

位级处理单元包括发射端的随机化、前向纠错(FEC)、到四相相移键控(QPSK)和正交调幅(QAM)功能的交织和变换。相应的接收处理位级单元包括符号解变换、解交织、FEC解码和解随机性。

除FEC译码外的所有位级功能都是相当简单的,而且计算不是密集的。例如,随机性包含数据位的模2加法(借助简单伪随机二进制时序产生器输出)。尽管FPGA比固定总线宽度的DSP能为位级处理提供更大的灵活性。但是,低计算复杂性允许DSP处理这些功能。相比,FEC译码包括Viterbi译码、Turbo卷积译码、Turbo乘积译码和LDPC译码是计算密集的,而且DSP处理时会消耗有效带宽。

FPGA广泛用于卸载这些功能。同样FPGA也可用到MAC层的接口,以实现一定的较低MAC功能(如加密/解密和鉴别)。

符号级处理

OFDMA中的符号级功能包括子信道化和解子信道化、信道判断、均衡和循环前缀插入以及消除功能。时间—频率变换和频率—时间变换,分别用于FFT和IFFT实现。

信道判断和均衡可以离线执行,这涉及更多有关控制算法,适合用DSP实现。相反,FFT和IFFT功能是规则的数据通路功能,这包括非常高速下的复杂乘法,适合于用FPGA实现。

图2示出包含在高端FPGA(Altera公司StratixⅡ器件)内的嵌入式DSP单元。DSP处理器通常有多达8个专用乘法器,而StratixⅡ器件有多达384专用乘法器,提供的吞吐量高达346GMAC,这比现有的DSP高出一个量级。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章