资料下载

×

基于DSP/FPGA的以太网控制器的设计方案

消耗积分:1 |

格式:rar |

大小:0.6 MB |

2017-10-26

运动控制技术是制造自动化的关键基础,其水平高低是衡量一个国家工业现代化的重要标志,研究和开发具有开放式结构的运动控制器是当前运动控制领域的一个重要发展方向。随着集成电路技术、微电子技术、计算机技术和网络技术的不断发展,运动控制器已从以单片机和微处理器作为核心的运动控制器和以专用芯片(ASIC)作为核心处理器的运动控制器,发展到了基于PC机平台的以数字信号处理器(DSP)和现场可编程门阵列(FPGA)作为核心处理器的协处理架构的开放式运动控制器。该控制器将PC机和DSP的信息处理能力与FPGA的外围扩展功能很好的结合在一起,具有信息处理能力强、模块化、开放程度高、运动轨迹控制精确等优点。

1系统概述

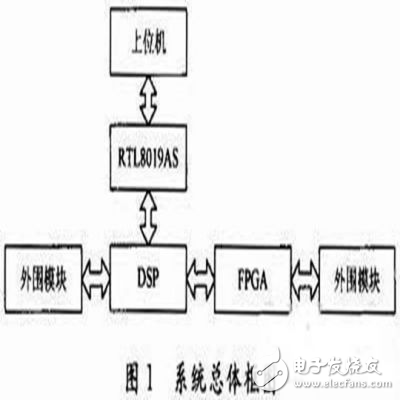

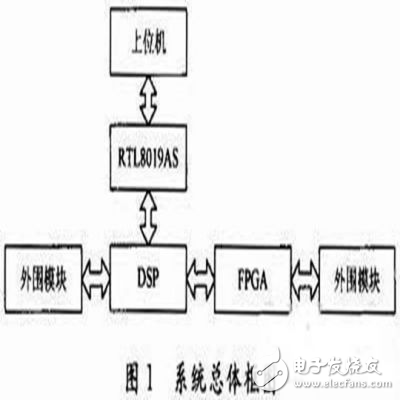

该四轴运动控制器系统以TI公司C2000系列DSP芯片TMS320F2812和alterA公司CycloneⅡ系列FPGA芯片EP2C8F256C6为核心,DSP通过网口接收上位机的控制参数,完成系统位置、速度控制及运动轨迹规划;FPGA完成运动控制器的精确插补功能和外围电路的扩展,系统总体框图如图1所示。

运动控制器的主要功能包括:4路模拟电压输出,电压范围为-10~+10V,分辨率为16b;4路脉冲量信号输出;4路脉冲方向信号输出;4路驱动复位信号输出;4路驱动使能信号输出;4路差分编码信号输入;4路驱动报警信号输入;8路正负限位信号输入;4路原点信号输入;16路通用数字量。I/O。

2DSP模块设计

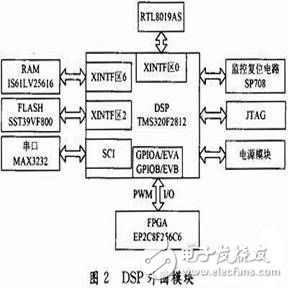

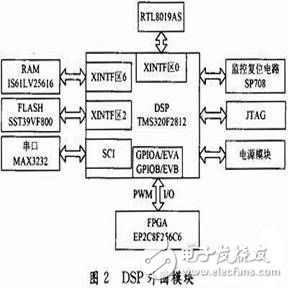

DSP根据从上位机接收的运动模式和运动参数实时计算规划位置和规划速度,生成所需的速度曲线,实时的输出规划位置。TMS320F2812是TI推出的一款专门用于电机控制的32位定点DSP芯片,采用高性能静态CMOS技术,主频高达150MHz(指令周期6.67ns),低功耗,核心电压为1.8V,I/O电压3.3V,支持JTAG边界扫描,128K×16b的片内FLASH。有两个事件管理器(EVA和EVB),它们都是特定的外围设备,为多轴运动控制器而设计的。可通过外部存储器接口XINTF扩展外部存储器。DSP外围模块设计如图2所示。

为增强抗干扰性,DSP通过以太网控制器RTL8019AS与上位机连接,RTL8019AS内部含有一个16KB的SDRAM,DSP通过外部存储器接口对其进行读写来接收上位机的命令或向上位机传送反馈信号。在数据处理过程中要占用大量的存储空间,DSP内部仅含有18K×16b的SARAM和128K×16b的FLASH,存储空间显得过小,所以通过外部接口扩展了256K×16bRAM和512K×16bFLASH,RAM和FLASH芯片分别选择IS61LV25616AL、SST39VF800,它们都具有接口简单、读写速度快等优点。SCI模块用于扩展RS232串行通信接口,串口芯片使用MAX3232。

运动控制器所需电压为5V,3.3V,1.8V,1.2V。输入电压5V,分别采用稳压芯片LM1085IS3.3,LM1117-1.8将其转换成3.3V和1.8V,由于TMS320F2812的I/O电压3.3V要先于内核电源上电,所以1.8V要由3.3V降压得到,以确保上电次序。1.2V是FPGA内核所需电压,由稳压芯片LM317S稳压得到,LM317S的输出电压范围为1.2~25V,复位电路采用SP708低功耗微处理器监控器件,此器件有众多的组件,有效的增强了系统的可靠性及工作效率。

1系统概述

该四轴运动控制器系统以TI公司C2000系列DSP芯片TMS320F2812和alterA公司CycloneⅡ系列FPGA芯片EP2C8F256C6为核心,DSP通过网口接收上位机的控制参数,完成系统位置、速度控制及运动轨迹规划;FPGA完成运动控制器的精确插补功能和外围电路的扩展,系统总体框图如图1所示。

运动控制器的主要功能包括:4路模拟电压输出,电压范围为-10~+10V,分辨率为16b;4路脉冲量信号输出;4路脉冲方向信号输出;4路驱动复位信号输出;4路驱动使能信号输出;4路差分编码信号输入;4路驱动报警信号输入;8路正负限位信号输入;4路原点信号输入;16路通用数字量。I/O。

2DSP模块设计

DSP根据从上位机接收的运动模式和运动参数实时计算规划位置和规划速度,生成所需的速度曲线,实时的输出规划位置。TMS320F2812是TI推出的一款专门用于电机控制的32位定点DSP芯片,采用高性能静态CMOS技术,主频高达150MHz(指令周期6.67ns),低功耗,核心电压为1.8V,I/O电压3.3V,支持JTAG边界扫描,128K×16b的片内FLASH。有两个事件管理器(EVA和EVB),它们都是特定的外围设备,为多轴运动控制器而设计的。可通过外部存储器接口XINTF扩展外部存储器。DSP外围模块设计如图2所示。

为增强抗干扰性,DSP通过以太网控制器RTL8019AS与上位机连接,RTL8019AS内部含有一个16KB的SDRAM,DSP通过外部存储器接口对其进行读写来接收上位机的命令或向上位机传送反馈信号。在数据处理过程中要占用大量的存储空间,DSP内部仅含有18K×16b的SARAM和128K×16b的FLASH,存储空间显得过小,所以通过外部接口扩展了256K×16bRAM和512K×16bFLASH,RAM和FLASH芯片分别选择IS61LV25616AL、SST39VF800,它们都具有接口简单、读写速度快等优点。SCI模块用于扩展RS232串行通信接口,串口芯片使用MAX3232。

运动控制器所需电压为5V,3.3V,1.8V,1.2V。输入电压5V,分别采用稳压芯片LM1085IS3.3,LM1117-1.8将其转换成3.3V和1.8V,由于TMS320F2812的I/O电压3.3V要先于内核电源上电,所以1.8V要由3.3V降压得到,以确保上电次序。1.2V是FPGA内核所需电压,由稳压芯片LM317S稳压得到,LM317S的输出电压范围为1.2~25V,复位电路采用SP708低功耗微处理器监控器件,此器件有众多的组件,有效的增强了系统的可靠性及工作效率。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章