资料下载

时间域中分析的时钟抖动,第 1 部分

仔细观察某个采样点,可以看到计时不准(时钟抖动或时钟相位噪声)是如何形

成振幅变化的。由于高 Nyquist 区域(例如,f1 = 10 MHz 到 f2 = 110 MHz)欠

采样带来输入频率的增加,固定数量的时钟抖动自理想采样点产生更大数量的振

幅偏差(噪声)。另外,图 2 表明时钟信号自身转换速率对采样时间的变化产生

了影响。转换速率决定了时钟信号通过零交叉点的快慢。换句话说,转换速率直

接影响 ADC 中时钟电路的触发阈值。

图 1 100MSPS 采样的两个输入信号显示了混叠带来的相同采样点

图 2 时钟抖动形成更多快速输入信号振幅误差

如果 ADC 的内部时钟缓冲器上存在固定数量的热噪声,则转换速率也转换为

计时不准,从而降低了 ADC 的固有窗口抖动。如图 3 所示,窗口抖动与时钟

抖动(相位噪声)没有一点关系,但是这两种抖动分量在采样时间组合在一起。

图 3 还表明窗口抖动随转换速率降低而增加。转换速率一般直接取决于时钟振

幅。

时钟抖动导致的 SNR 减弱

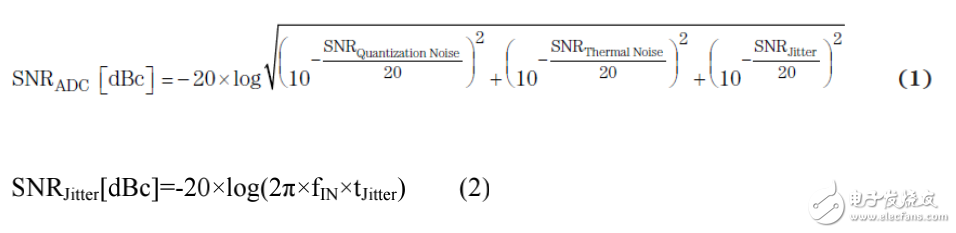

有几个因素会限制 ADC 的 SNR,例如:量化噪声(管线式转换器中一般不明

显)、热噪声(其在低输入频率下限制 SNR),以及时钟抖动(SNRJitter)(请参

见下面方程式 1)。SNRJitter 部分受到输入频率 fIN(取决于 Nyquist 区域)的限

制,同时受总时钟抖动量 tJitter 的限制,其计算方法如下:

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章