资料下载

×

FPGA+DSP导引头信号处理中FPGA设计的关键技术解析

消耗积分:1 |

格式:rar |

大小:0.5 MB |

2017-11-01

1 引言

随着同防工业对精确制导武器要求的不断提高,武器系统总体设计方案的日趋复杂,以及电子元器件水平的飞速发展。导引头信号处理器的功能越来越复杂,硬件规模越来越大.处理速度也越来越高.而且产品的更新速度加快,生命周期缩短。实现功能强、性能指标高、抗干扰能力强、工作稳定可靠、体积小、功耗低、结构紧凑合理符合弹载要求的导引头信号处理器已经势在必行。过去单一采用DSP处理器搭建信号处理器已经不能满足要求.FPGA+DSP的导引头信号处理结构成为当前以及未来一段时间的主流。

FPGA和DSP处理器具有截然不同的架构,在一种器件上非常有效的算法.在另一种器件上可能效率会非常低。如果目标要求大量的并行处理或者最大的多通道流量,那么单纯基于DSP的硬件系统就可能需要更大的面积,成本或功耗。一个FPGA仅在一个器件上就能高提供多达550个并行乘法和累加运算,从而以较少的器件和较低的功耗提供同样的性能。但对于定期系数更新,决策控制任务或者高速串行处理任务,FPGA的优化程度远不如DSP。

FPGA+DSP的数字硬件系统正好结合了两者的优点,兼顾了速度和灵活性。本文以导引头信号处理系统为例说明FPGA+DSP系统中FPGA的关键技术。

2 系统组成

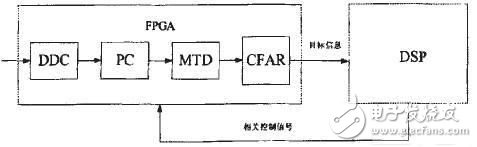

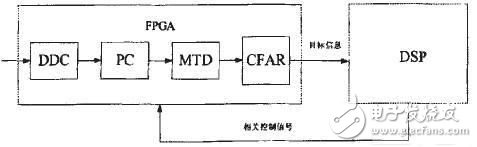

本系统南一片FPGA和一片DSP来组成,FPGA在实时并行计算实现标准数字信号处理算法的能力远强于DSP,因此数字接收系统信号处理要用到的FIR滤波、FFT、IFFT等算法,在FPGA中实现要远快于用DSP,且FPGA厂商提供了非常丰富易用的能实现数字信号处理的参数Core.可以大大简化开发过程。而且,FPGA支持丁程师设计高度并行的架构以及有大量乘法器和存储器资源,因此将数字下变频(DDC),脉压(PC),动目标检测(MTD),恒虚警处理(CFAR)等也在FPGA中实现,可有效提高实时性,集成度和稳定性。而DSP用来进行其他复杂信号处理,比如自动目标识别、抗干扰等。

FPGA和DSP的通信通过32位的数据总线联通。FPGA通过此数据总线把柃测得到的目标信息传递给DSP做后续处理,DSP则通过数据总线传递控制信息。

图1 FPGA+DSP的系统组成框图

3 FPGA设计中的关键技术

3.1 跨时钟域的设计

3.1.1基础

只有最初级的逻辑电路才使用单一的时钟。大多数与数据传输相关的应用都有与牛俱来的挑战,即跨越多个时钟域的数据移动,例如磁盘控制器、CDROM/DVD控制器、调制解调器、网卡以及网络处理器等。当信号从一个时钟域传送到另一个时钟域时,出现在新时钟域的信号是异步信号。

在现代IC、ASIC以及FPGA设计中,许多软件程序可以帮助工程师建立几百万门的电路。但这些程序都无法解决信号同步问题。设计者需要了解可靠的设计技巧,以减少电路在跨时钟域通信时的故障风险。

从事多时钟设计的第一步是要理解信号稳定性问题。当一个信号跨越某个时钟域时.对新时钟域的电路来说它就是一个异步信号。接收该信号的电路需要对其进行同步。同步可以防止第一级存储单元(触发器)的亚稳态在新的时钟域里传播蔓延。

亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。当一个触发器进入亚稳态时,既尤法预测该单元的输}}{电平,也无法预测何时输出才能稳定在某个正确的电平上。在这个稳定期问,触发器输出一些中间级电平,或者可能处于振荡状态,并且这种尤用的输出电平可以滑信号通道上的各个触发器级联式传播下去。

由于数据率比较低,而FPGA的工作频率可以很高,所以在雷达信号处理机的FPGA设计中,势必要引入跨时钟域的设计,例如在某项口中,控制网络为10M.脉冲压缩工作时钟为200M,MTD、CFAR为80M,是个典型的跨时钟域设计。

随着同防工业对精确制导武器要求的不断提高,武器系统总体设计方案的日趋复杂,以及电子元器件水平的飞速发展。导引头信号处理器的功能越来越复杂,硬件规模越来越大.处理速度也越来越高.而且产品的更新速度加快,生命周期缩短。实现功能强、性能指标高、抗干扰能力强、工作稳定可靠、体积小、功耗低、结构紧凑合理符合弹载要求的导引头信号处理器已经势在必行。过去单一采用DSP处理器搭建信号处理器已经不能满足要求.FPGA+DSP的导引头信号处理结构成为当前以及未来一段时间的主流。

FPGA和DSP处理器具有截然不同的架构,在一种器件上非常有效的算法.在另一种器件上可能效率会非常低。如果目标要求大量的并行处理或者最大的多通道流量,那么单纯基于DSP的硬件系统就可能需要更大的面积,成本或功耗。一个FPGA仅在一个器件上就能高提供多达550个并行乘法和累加运算,从而以较少的器件和较低的功耗提供同样的性能。但对于定期系数更新,决策控制任务或者高速串行处理任务,FPGA的优化程度远不如DSP。

FPGA+DSP的数字硬件系统正好结合了两者的优点,兼顾了速度和灵活性。本文以导引头信号处理系统为例说明FPGA+DSP系统中FPGA的关键技术。

2 系统组成

本系统南一片FPGA和一片DSP来组成,FPGA在实时并行计算实现标准数字信号处理算法的能力远强于DSP,因此数字接收系统信号处理要用到的FIR滤波、FFT、IFFT等算法,在FPGA中实现要远快于用DSP,且FPGA厂商提供了非常丰富易用的能实现数字信号处理的参数Core.可以大大简化开发过程。而且,FPGA支持丁程师设计高度并行的架构以及有大量乘法器和存储器资源,因此将数字下变频(DDC),脉压(PC),动目标检测(MTD),恒虚警处理(CFAR)等也在FPGA中实现,可有效提高实时性,集成度和稳定性。而DSP用来进行其他复杂信号处理,比如自动目标识别、抗干扰等。

FPGA和DSP的通信通过32位的数据总线联通。FPGA通过此数据总线把柃测得到的目标信息传递给DSP做后续处理,DSP则通过数据总线传递控制信息。

图1 FPGA+DSP的系统组成框图

3 FPGA设计中的关键技术

3.1 跨时钟域的设计

3.1.1基础

只有最初级的逻辑电路才使用单一的时钟。大多数与数据传输相关的应用都有与牛俱来的挑战,即跨越多个时钟域的数据移动,例如磁盘控制器、CDROM/DVD控制器、调制解调器、网卡以及网络处理器等。当信号从一个时钟域传送到另一个时钟域时,出现在新时钟域的信号是异步信号。

在现代IC、ASIC以及FPGA设计中,许多软件程序可以帮助工程师建立几百万门的电路。但这些程序都无法解决信号同步问题。设计者需要了解可靠的设计技巧,以减少电路在跨时钟域通信时的故障风险。

从事多时钟设计的第一步是要理解信号稳定性问题。当一个信号跨越某个时钟域时.对新时钟域的电路来说它就是一个异步信号。接收该信号的电路需要对其进行同步。同步可以防止第一级存储单元(触发器)的亚稳态在新的时钟域里传播蔓延。

亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。当一个触发器进入亚稳态时,既尤法预测该单元的输}}{电平,也无法预测何时输出才能稳定在某个正确的电平上。在这个稳定期问,触发器输出一些中间级电平,或者可能处于振荡状态,并且这种尤用的输出电平可以滑信号通道上的各个触发器级联式传播下去。

由于数据率比较低,而FPGA的工作频率可以很高,所以在雷达信号处理机的FPGA设计中,势必要引入跨时钟域的设计,例如在某项口中,控制网络为10M.脉冲压缩工作时钟为200M,MTD、CFAR为80M,是个典型的跨时钟域设计。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章