资料下载

×

多核TMS320C6474中串行协议RapiIO性能优化

消耗积分:1 |

格式:rar |

大小:0.92 MB |

2017-11-02

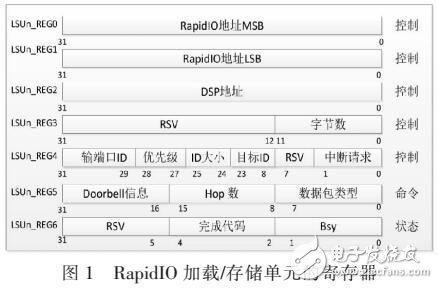

现今的处理器性能很强大,可以提供很高计算速度,但是对其处理能力的某些应用要求也在不断增加。这就产生了拥有处理器的机器同时T作的概念。但是这种多个机器同时T作的机制需要解决两个基本的相互关联的问题:处理器间通信和处理器与其它信息处理部分之间的通信。为了解决处理器之间的互连问题,并满足嵌入式系统对带宽不断增长的需求,提出了串行Rapidl0( SRIO)互连协议。这种结构起初是为嵌入式计算系统设计的,如今应用到边缘网络,存储,军事和丁业设备等各个领域。文中提出的对集成在DSP-TMS320C6474上的串行互连Rapidl0的性能优化结果,是以C6474作为实验平台的。这个板子上有两个DSP处理器,通过一条串行Rapidl0总线上的两个通道相连。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章