资料下载

×

6核DSP加快LTE配置级别及下一代无线标准

消耗积分:1 |

格式:rar |

大小:0.5 MB |

2017-11-03

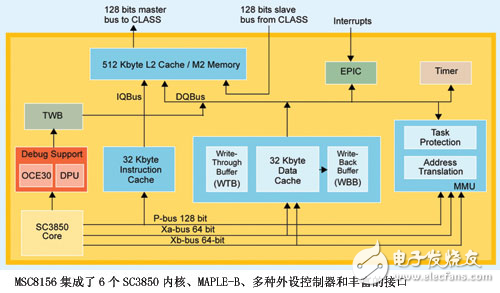

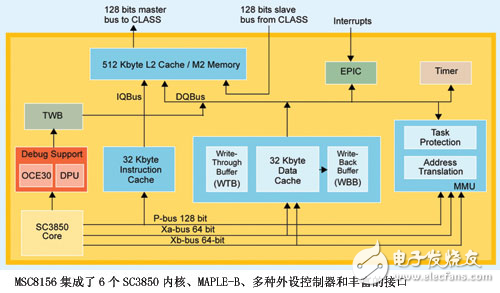

下一代的无线通信标准LTE在提供高数据速率的同时,对系统成本、数字信号处理能力提出了更高的要求。飞思卡尔半导体公司推出的6核DSP MSC8156采用SC3850 StarCore DSP内核和45nm工艺,处理能力高达48000MMACS,是4核DSP MSC8144处理性能的两倍,2个用于在系统存储器和处理器内核间传送数据的主总线的吞吐量高达50Gbps,可大幅提高无线宽带基站设备功能,并提供主流及最新网络配置所要求的灵活性、集成性及经济性。

强劲的内核

每个StarCore DSP SC3850内核的时钟频率为1GHz,每个内核都有4个ALU,每个ALU具有2个16×16 MAC,在1GHz频率下,每个ALU每秒可执行80亿次乘累加操作,即8000(MMACS),使MSC8156的总处理能力高达48000MMACS。每个内核具有32KB的8-way L1指令缓存、32KB的8-way L1数据缓存、512KB的8-way L2统一的指令/数据缓存(可配置成M2存储器)、存储器管理单元(MMU)、增强的可编程中断控制器(EPIC)、调试和分析单元(DPU)、2个32位定时器。处理器的内核电压为1V,I/O电压为1.0V、1.5 V、1.8V和2.5V。

MSC8156在6次迭代的Turbo编码时的性能为200Mbps,在K=9(zero tail)的Viterbi编码时的性能为115Mbp,在执行128、256、512、1024或2048点的FFT/iFFT变换时的采样率为每秒3.5亿次,1536点的DFT/iDFT变换时的采样率为每秒1.75亿次。

丰富的集成资源

MSC8156内部集成了32通道的DMA控制器;2个时钟为400MHz的DDR控制器;2个频率高达500MHz的RISC内核QUICC引擎可独立于DSP内核实现并行的包处理;1056KB共享的M3存储器;2个DDR控制器;2个serial RapidIO接口;2个千兆位以太网控制器;1个PCI-Express控制器;4个256通道时分复用(TDM)接口;1个16位双向通道DMA控制器;1个SPI接口;1个UART接口和I2C接口;支持2个4x SerDes端口的HSSI;4个TDM接口,UART和I2C接口;8个软件看门狗定时器;16个16位定时器;8个硬件信号量;32个可复用接口信号和IRQ输入的端口;3个输入时钟和5个PLL,符合IEEE标准的JTAG测试接入端口(TAP)和边界扫描架构,有等待、停止和断电三种低功耗待机模式,优化的电源管理电路。

MSC8156DSP针对基带(称为MAPLE-B)提供的在线多加速器平台引擎技术,与6个完全可编程的DSP内核一起操作,以支持3G-LTE、TDD-LTE、TD-SCDMA和WiMAX标准,并且达到HSPA和HSPA+的码速率。在单个平台上实现多标准功能,就不再需要根据不同基站标准重新设计硬件,因此该器件可在宏(Macro)基站、微(Micro)基站和微微(Pico)基站的不同尺寸之间进行扩展。MAPLE-B包括Turbo、 Viterbi、FFT及DFT处理引擎和两个可配置RISC引擎,这些引擎以后可以重新编程,以满足更新需求。

强劲的内核

每个StarCore DSP SC3850内核的时钟频率为1GHz,每个内核都有4个ALU,每个ALU具有2个16×16 MAC,在1GHz频率下,每个ALU每秒可执行80亿次乘累加操作,即8000(MMACS),使MSC8156的总处理能力高达48000MMACS。每个内核具有32KB的8-way L1指令缓存、32KB的8-way L1数据缓存、512KB的8-way L2统一的指令/数据缓存(可配置成M2存储器)、存储器管理单元(MMU)、增强的可编程中断控制器(EPIC)、调试和分析单元(DPU)、2个32位定时器。处理器的内核电压为1V,I/O电压为1.0V、1.5 V、1.8V和2.5V。

MSC8156在6次迭代的Turbo编码时的性能为200Mbps,在K=9(zero tail)的Viterbi编码时的性能为115Mbp,在执行128、256、512、1024或2048点的FFT/iFFT变换时的采样率为每秒3.5亿次,1536点的DFT/iDFT变换时的采样率为每秒1.75亿次。

丰富的集成资源

MSC8156内部集成了32通道的DMA控制器;2个时钟为400MHz的DDR控制器;2个频率高达500MHz的RISC内核QUICC引擎可独立于DSP内核实现并行的包处理;1056KB共享的M3存储器;2个DDR控制器;2个serial RapidIO接口;2个千兆位以太网控制器;1个PCI-Express控制器;4个256通道时分复用(TDM)接口;1个16位双向通道DMA控制器;1个SPI接口;1个UART接口和I2C接口;支持2个4x SerDes端口的HSSI;4个TDM接口,UART和I2C接口;8个软件看门狗定时器;16个16位定时器;8个硬件信号量;32个可复用接口信号和IRQ输入的端口;3个输入时钟和5个PLL,符合IEEE标准的JTAG测试接入端口(TAP)和边界扫描架构,有等待、停止和断电三种低功耗待机模式,优化的电源管理电路。

MSC8156DSP针对基带(称为MAPLE-B)提供的在线多加速器平台引擎技术,与6个完全可编程的DSP内核一起操作,以支持3G-LTE、TDD-LTE、TD-SCDMA和WiMAX标准,并且达到HSPA和HSPA+的码速率。在单个平台上实现多标准功能,就不再需要根据不同基站标准重新设计硬件,因此该器件可在宏(Macro)基站、微(Micro)基站和微微(Pico)基站的不同尺寸之间进行扩展。MAPLE-B包括Turbo、 Viterbi、FFT及DFT处理引擎和两个可配置RISC引擎,这些引擎以后可以重新编程,以满足更新需求。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章